Die LPC80x von NXP Semiconductors bilden eine kostengünstige Familie Arm-Cortex-M0+-basierter 32-Bit-MCU mit CPU-Frequenzen von bis zu 15 MHz. Die Produktfamilie LPC80x ist Teil der EdgeVerse™-Edge-Computing-Plattform von NXP. Die MCU-Familie LPC80x unterstützt bis zu 32 KB Flash-Speicher und bis zu 4 KB SRAM.

Die LPC80x von NXP Semiconductors bilden eine kostengünstige Familie Arm-Cortex-M0+-basierter 32-Bit-MCU mit CPU-Frequenzen von bis zu 15 MHz. Die Produktfamilie LPC80x ist Teil der EdgeVerse™-Edge-Computing-Plattform von NXP. Die MCU-Familie LPC80x unterstützt bis zu 32 KB Flash-Speicher und bis zu 4 KB SRAM.

Diese Familie verfügt über einen leistungsoptimierten Kern, geringen Platzbedarf in gängigen Gehäusen und Pegelwandlungsoptionen dank ihrer separaten Versorgungsschienen. Das Peripheriepaket der Serie LPC80x umfasst eine CRC-Engine, I2C-Bus-Schnittstellen, bis zu 2 USART, eine SPI, eine kapazitive Touch-Schnittstelle (Cap Touch), einen Timer mit mehreren Raten, einen Timer zur automatischen Aktivierung, einen allgemeinen 32-Bit-Counter/Timer, einen 12-Bit-ADW, einen 10-Bit-DAW, einen Analog-Komparator, E/A-Ports mit per Schaltmatrix konfigurierbarer Funktion, eine Engine zur Abstimmung der Eingangsmuster, eine programmierbare Logikeinheit (PLU) und bis zu 30 GPIO-Pins.

| Merkmale |

- System

- Arm-Cortex-M0+-Prozessor (Revision r0p1) mit Betriebsfrequenzen von bis zu 15 MHz, Einzelzyklus-Multiplikator und schnellem einzykligen E/A-Port; integrierter Nested Vectored Interrupt Controller (NVIC)

- Systemtaktgeber

- Mehrschichtige AHB-Matrix

- Serial Wire Debug (SWD) mit vier Haltepunkten und zwei Überwachungspunkten; Unterstützung von JTAG Boundary Scan Description Language (BSDL)

- Digitale Peripheriegeräte

- High-Speed-GPIO-Schnittstelle verbunden mit Arm-Cortex-M0+-E/A-Bus mit bis zu 30 GPIO-Pins mit konfigurierbaren Pull-up-/Pull-Down-Widerständen, programmierbarem Open-Drain-Modus und Eingangswechselrichter; GPIO-Richtungssteuerung unterstützt unabhängiges Einstellen/Löschen/Umschalten individueller Bits

- Hochstrom-Quellen-Ausgangstreiber (20 mA) an drei Pins

- Fähigkeit zu GPIO-Interrupt-Generation mit Boolescher Musterabstimmfunktion an acht GPIO-Eingängen (LPC804)

- Schaltmatrix für flexible Konfiguration der Funktion jedes E/A-Pins

- CRC-Engine

- Kapazitive Touch-Funktion (LPC804)

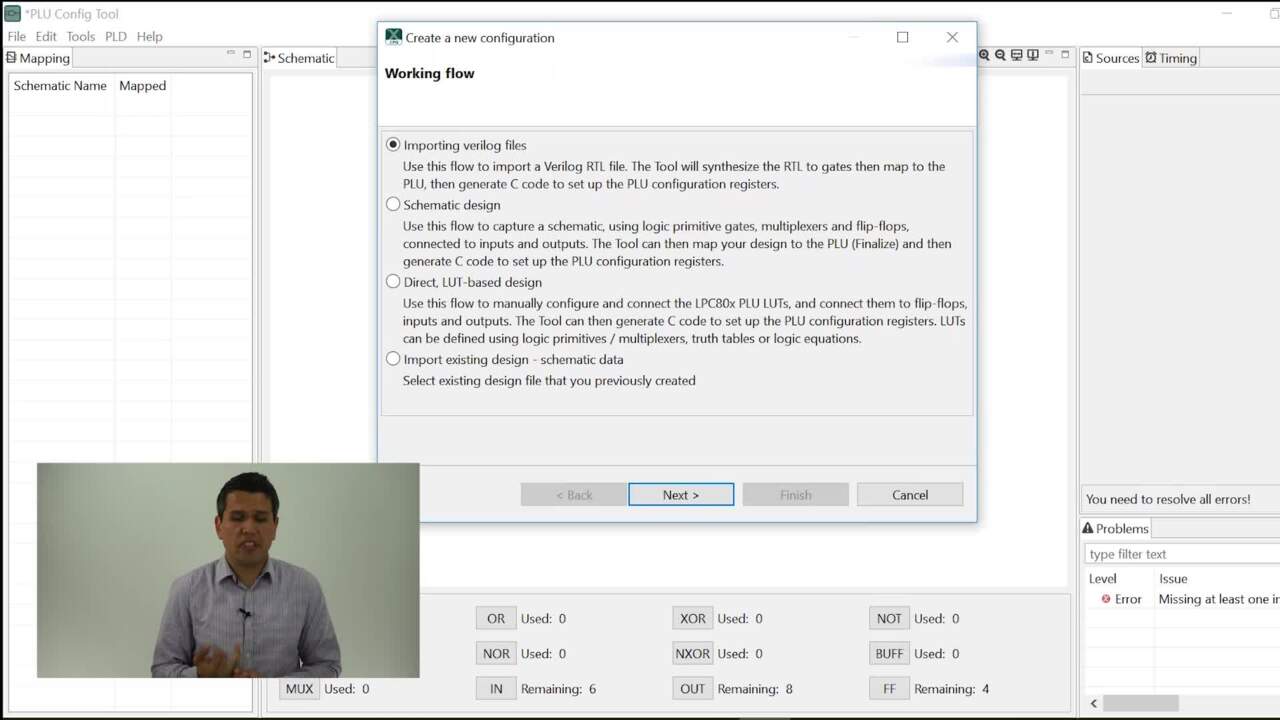

- PLU zur Erstellung kleiner kombinatorischer und/oder sequenzieller Logiknetzwerke, einschließlich einfacher Zustandsautomaten (LPC804)

|

|

- ROM-API-Unterstützung

- Bootloader

- Unterstützung von Flash-in-Application-Programmierung (IAP)

- Unterstützung von In-System-Programmierung (ISP) über USART

- On-Chip-ROM-API für Integer-Teiler

- API freischwingender Oszillator (FRO)

- Speicher

- Bis zu 32 KB Flash-Programmierspeicher im Chip

- Code-Leseschutz (CRP)

- Bis zu 4 KB SRAM

- Duale E/A-Leistung (LPC802M011JDH20, LPC804M111JDH24):

- Unabhängige Versorgung auf jeder Gehäuseseite, die Signal mit Pegelverschiebung von einem chipexternen Spannungsbereich zu einem anderen und/oder direkte Anbindung chipexterner Peripheriekomponenten mit abweichenden Versorgungspegeln erlaubt

|

| Anwendungen |

- Sensor-Gateways

- Industrielle Anwendungen

- Gaming-Controller

- 8-/16-Bit-Anwendungen

- Verbraucherelektronik

|

|

- Klimaüberwachung

- Motorsteuerungen

- Tragbare Geräte und Wearables

- Beleuchtung

- Brandschutz- und Sicherheitssysteme

|

![]() Die LPC80x von NXP Semiconductors bilden eine kostengünstige Familie Arm-Cortex-M0+-basierter 32-Bit-MCU mit CPU-Frequenzen von bis zu 15 MHz. Die Produktfamilie LPC80x ist Teil der EdgeVerse™-Edge-Computing-Plattform von NXP. Die MCU-Familie LPC80x unterstützt bis zu 32 KB Flash-Speicher und bis zu 4 KB SRAM.

Die LPC80x von NXP Semiconductors bilden eine kostengünstige Familie Arm-Cortex-M0+-basierter 32-Bit-MCU mit CPU-Frequenzen von bis zu 15 MHz. Die Produktfamilie LPC80x ist Teil der EdgeVerse™-Edge-Computing-Plattform von NXP. Die MCU-Familie LPC80x unterstützt bis zu 32 KB Flash-Speicher und bis zu 4 KB SRAM.