Verwenden Sie FPGAs zum Erstellen eingebetteter High-Performance-Bildverarbeitungsanwendungen mit maschinellem Lernen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2018-09-06

Das schnelle Wachstum der von Kameras und anderen Geräten stammenden Datenmengen hat dazu geführt, dass maschinelles Lernen (ML) unter anderem in der Automobil- und Sicherheitstechnik zur Extraktion nützlicherer Informationen aus Bildern eingesetzt wird. Spezialisierte Geräte versprechen High-Performance-ML-Inferenz in eingebetteten Bildverarbeitungsanwendungen. Viele dieser Geräte sind noch in den frühesten Entwicklungsstadien und die Entwickler suchen nach den besten Algorithmen, während sich im Bereich der künstlichen Intelligenz (KI) in rasantem Tempo neue Methoden entwickeln.

Heute nutzen Entwickler FPGA-basierte Plattformen für ML zum Erstellen von eingebetteten Bildverarbeitungssystemen, die den gestiegenen Leistungsanforderungen gewachsen sind. Zugleich ist genug Flexibilität möglich, um mit den Fortschritten beim maschinellen Lernen Schritt zu halten.

Dieser Artikel beschreibt die Anforderungen einer ML-Verarbeitung und warum FPGAs viele der Leistungsprobleme lösen. Anschließend wird eine geeignete FPGA-basierte ML-Plattform vorgestellt und ihre Verwendung erläutert.

Algorithmen und Inferenz-Engines für maschinelles Lernen

Bei den ML-Algorithmen haben sich faltungsneuronale Netzwerke (Convolutional Neural Networks – CNNs) als bevorzugte Lösung für die Bildklassifizierung durchgesetzt. Weil sie hohe Genauigkeitsraten in der Bilderkennung erreichen, werden sie in einer Vielzahl von Anwendungen plattformübergreifend für Smartphones, Sicherheitssysteme und Fahrerassistenzsysteme der Automobiltechnik eingesetzt. CNNs sind ein Typ der tiefen neuronalen Netzwerke (Deep Neural Network – DNN) und verwenden als solche eine neuronale Netzwerkarchitektur mit spezialisierten Schichten, die Merkmale aus Bildern extrahieren und diese Merkmale dazu verwenden, beim Training mit beschrifteten Bildern Bilder zu klassifizieren (siehe „Get Started with Machine Learning Using Readily Available Hardware and Software“ (Einstieg in das maschinelle Lernen mit verfügbarer Hardware und Software)).

CNN-Entwickler führen in der Regel ein Training auf High-Performance-Systemen oder Cloud-Plattformen durch und verwenden Grafikprozessoren (GPUs), um die große Anzahl an Matrixberechnungen, die für das Training von Modellen mit beschrifteten Bilddatensätzen erforderlich sind und oft im Millionenbereich liegen, zu beschleunigen. Nach dem Training wird das trainierte Modell in Inferenzanwendungen verwendet, zur Klassifizierung neuer Bilder oder Frames aus Videostreams. Für Inferenz eingesetzt, muss ein trainiertes Modell immer noch dieselben Matrixberechnungen durchführen, aber weil das Inputvolumen so viel kleiner ist, können Entwickler CNNs für kleinere ML-Anwendungen einsetzen, die auf Universalhardware laufen (siehe „Entwicklung einer Anwendung für maschinelles Lernen mit dem Raspberry Pi“).

Für viele Anwendungen fehlt Universalplattformen jedoch die Leistung, die erforderlich ist, um bei CNN-Inferenz eine hohe Genauigkeit und Leistung zugleich zu erzielen. Optimierungstechniken und alternative CNN-Architekturen wie MobileNet oder SqueezeNet reduzieren die Plattformanforderungen, aber das geschieht in der Regel auf Kosten der Genauigkeit und Inferenzlatenz, was unter Umständen nicht mit den Anwendungsanforderungen vereinbar ist.

Zugleich verkompliziert die rasante Weiterentwicklung der Algorithmen die Entwicklung von ICs für maschinelles Lernen; diese sollten so stark spezialisiert sein, dass die Inferenz beschleunigt wird, und doch so universell sein, dass sie neue Algorithmen unterstützen. Jahrelang haben FPGAs genau diese Rolle erfüllt: die Kombination aus Leistung und Flexibilität bereitzustellen, die erforderlich ist, um kritische Algorithmen zu beschleunigen, wenn Universalprozessoren nicht ausreichend oder spezialisierte Geräte nicht verfügbar sind.

FPGAs als Plattformen für maschinelles Lernen

Für maschinelles Lernen setzen GPUs weiterhin Maßstäbe – Maßstäbe, die frühere FPGAs nicht einmal annähernd erreichen konnten. Neuere Geräte wie das FPGA Arria 10 GX von Intel und das FPGA ECP5 von Lattice Semiconductor haben den Abstand zwischen FPGAs und GPUs deutlich verkleinert. Für manche DNN-Architekturen mit kompakten ganzzahligen Datentypen kann diese FPGA-Klasse sogar mehr Leistung / höhere Wattzahlen als eine Standard-GPU liefern.

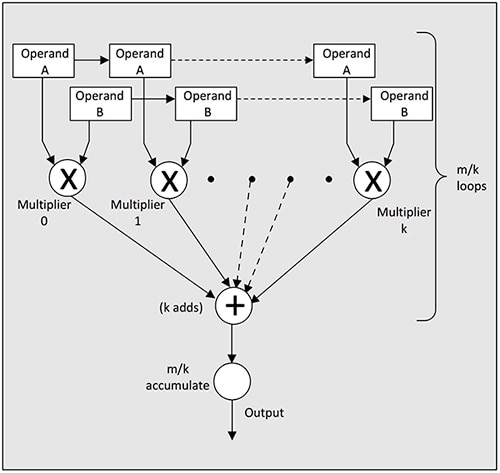

Hochentwickelte FPGAs erreichen dank ihrer Kombination aus eingebettetem Speicher und Ressourcen für digitale Signalverarbeitung (DSP) hohe Leistungen bei allgemeinen Matrix-Multiplikationen (GEMM). Die Möglichkeit, eingebetteten Speicher nahe an den Berechnungsengines zu platzieren, entschärft den CPU-Speicherengpass, der die Leistung von Algorithmen für maschinelles Lernen auf Universalprozessoren beschränken kann. Eingebettete DSP-Berechnungsengines auf FPGAs wiederum bieten eine größere Anzahl paralleler Multiplikatorressourcen als selbst auf typischen DSP-Geräten verfügbar sind (Abbildung 1). FPGA-Lieferanten bieten FPGA-Entwicklungsplattformen speziell für maschinelles Lernen an und schöpfen damit die Vorteile dieser Merkmale voll aus.

Abbildung 1: Hochentwickelte FPGAs wie das ECP5 von Lattice Semiconductor bieten eine Kombination aus Parallelverarbeitungsressourcen und eingebettetem Speicher für High-Performance-Inferenz. (Bildquelle: Lattice Semiconductor)

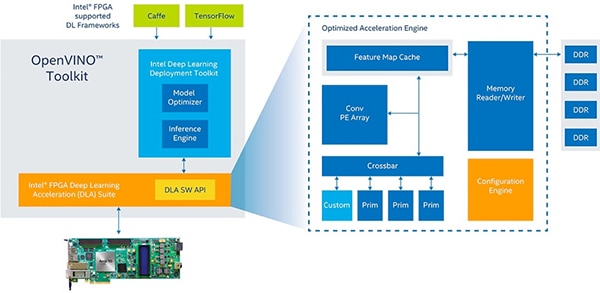

Der seit Kurzem erhältliche OPENVINO™ mit FPGA-Unterstützung von Intel beispielsweise erweitert die Möglichkeiten dieser Plattform, um Inferenzmodelle für verschiedene Geräte bereitzustellen, einschließlich GPUs, CPUs und FPGAs. Hier arbeiten Entwickler mit Intels Deep Learning Inferenz-Engine-Workflow, der das Deep Learning Deployment Toolkit von Intel und das Intel Computer Vision Softwareentwicklungskit (SDK) im Intel OPENVINO-Toolkit miteinander kombiniert. Entwickler verwenden die Anwendungsprogrammierschnittstelle (API) des SDK, um mithilfe von Intels Run-Model-Optimizer ein Modell zu erstellen, das auf diese verschiedenen Hardwareplattformen ausgerichtet werden kann.

Auf das Intel-Entwicklungskit DK-DEV-10AX115S-A für Arria-10-GX-FPGAs ausgerichtet, ermöglicht das Deep Learning Deployment Toolkit Entwicklern den Import trainierter Modelle aus führenden ML-Frameworks, einschließlich Caffe und TensorFlow (Abbildung 2). Innerhalb des Toolkits handhaben der Model Optimizer und die Inference Engine die Modellkonvertierung bzw. -bereitstellung auf einer Zielplattform wie dem Arria-10-GX-FPGA-Entwicklungskit oder einem benutzerdefinierten Design unter Verwendung einer Arria-10-GX-FPGA-Komponente.

Abbildung 2: Das OPENVINO-Toolkit mit FPGA-Unterstützung von Intel bietet eine vollständige Toolkette für die Bereitstellung von Modellen auf Caffe, TensorFlow und anderen Frameworks im Arria-10-GX-FPGA-Entwicklungskit oder benutzerdefinierten Designs um das Arria-10-GX-FPGA. (Bildquelle: Intel)

Für die Migration eines bereits trainierten Modells verwenden Entwickler den Python-basierten Model Optimizer, um eine in einer xml-Datei enthaltene Zwischendarstellung (Intermediate Representation – IR) zu generieren, die die Netzwerktopologie und eine Bin-Datei bereitstellt. Diese enthält die Modellparameter als Binärwerte. Neben der Erstellung der IR übt der Model Optimizer eine kritische Funktion bei der Entfernung von Schichten aus, die im Modell für das Training benötigt werden, nicht aber für Inferenz. Zudem führt das Tool Schichten zusammen, die jeweils separate mathematische Operationen, wenn möglich in einer einzigen kombinierten Schicht zusammenführen.

Das Ergebnis dieser Netzwerkbereinigung und -zusammenführung ist ein kompakteres Modell, das wiederum kürzere Inferenzzeiten und geringere Speicheranforderungen für die Zielplattform mit sich bringt.

Die Intel Inference Engine ist eine C++-Bibliothek mit einem Satz C++-Klassen, die in der unterstützten Ziel-Hardwareplattform gemeinsam verwendet werden, um Inferenz auf der Plattform zu ermöglichen. Für die Inferenzanwendung verwenden Entwickler Klassen wie CNNNetReader, um die CNN-Topologie, die in der xml-Datei enthalten ist (ReadNetwork), und die Modellparameter, die in der Bin-Datei enthalten sind (ReadWeights), zu lesen. Ist das Laden des Modells abgeschlossen, führt ein Aufruf der Klassenmethode Infer() eine blockierende Inferenz aus, während ein Aufruf der Klassenmethode StartAsync() eine Inferenz asynchron ausführt und eine Warte- oder Completion-Routine ausführt, um die Ergebnisse nach Abschluss der Inferenz zu handhaben.

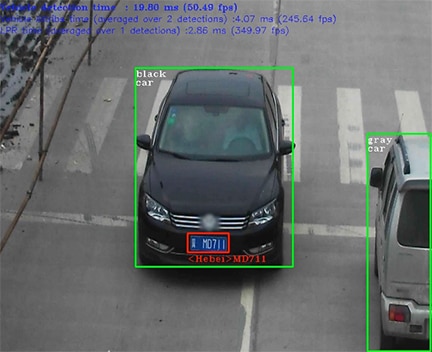

Intel demonstriert den vollständigen Workflow und detaillierte Inference Engine API-Aufrufe in einer Reihe von Beispielanwendungen, die in der OPENVINO-Umgebung verfügbar sind. Eine Beispielanwendung für Sicherheitsbarrierenkameras veranschaulicht die Verwendung einer Pipeline aus Inferenzmodellen, um zunächst eine Fahrzeug-Bounding-Box zu identifizieren (Abbildung 3). Das nächste Modell in der Pipeline untersucht den Inhalt dieser Bounding-Box, um Fahrzeugeigenschaften wie Fahrzeugklasse, Farbe und Ort des Kennzeichens zu ermitteln.

Abbildung 3: Die Beispielanwendung für Sicherheitsbarrierenkameras von Intel zeigt die Verwendung einer Inferenz-Pipeline zur Identifizierung eines Fahrzeugs (grüne Bounding-Box), Ermittlung von Fahrzeugeigenschaften wie Farbe, Typ und Ort des Kennzeichens (roter Kasten) und schließlich Ermittlung der Zeichen auf dem Kennzeichen (roter Text). (Bildquelle: Intel Corp.)

Das letzte Modell in der Pipeline verwendet diese Fahrzeugeigenschaften, um die Buchstaben des Kennzeichens zu extrahieren. Um das Modell für Inferenz zu nutzen, zeigt der Beispielcode die Verwendung der Inference Model C++-Bibliothek zum Erstellen eines Objekts (LPR), das eine Instanz einer Struktur mit der Bezeichnung LPRDetection ist. Diese Struktur verwendet Objekte der Inference Engine API-Klasse, um zu lesen (CNNNetReader) und Modelleingaben und -ausgaben zu validieren (Listing 1).

Kopieren CNNNetwork read() override { std::cout << "[ INFO ] Loading network files for Licence Plate Recognition (LPR)" << std::endl; CNNNetReader netReader; /** Read network model **/ netReader.ReadNetwork(FLAGS_m_lpr); std::cout << "[ INFO ] Batch size is forced to 1 for LPR Network" << std::endl; netReader.getNetwork().setBatchSize(1); /** Extract model name and load it's weights **/ std::string binFileName = fileNameNoExt(FLAGS_m_lpr) + ".bin"; netReader.ReadWeights(binFileName); /** LPR network should have 2 inputs (and second is just a stub) and one output **/ // ---------------------------Check inputs std::cout << "[ INFO ] Checking LPR Network inputs" << std::endl; InputsDataMap inputInfo(netReader.getNetwork().getInputsInfo()); if (inputInfo.size() != 2) { throw std::logic_error("LPR should have 2 inputs"); } InputInfo::Ptr& inputInfoFirst = inputInfo.begin()->second; inputInfoFirst->setInputPrecision(Precision::U8); inputInfoFirst->getInputData()->setLayout(Layout::NCHW); inputImageName = inputInfo.begin()->first; auto sequenceInput = (++inputInfo.begin()); inputSeqName = sequenceInput->first; if (sequenceInput->second->getTensorDesc().getDims()[0] != maxSequenceSizePerPlate) { throw std::logic_error("LPR post-processing assumes certain maximum sequences"); } // ---------------------------Check outputs std::cout << "[ INFO ] Checking LPR Network outputs" << std::endl; OutputsDataMap outputInfo(netReader.getNetwork().getOutputsInfo()); if (outputInfo.size() != 1) { throw std::logic_error("LPR should have 1 output"); } outputName = outputInfo.begin()->first; std::cout << "[ INFO ] Loading LPR model to the "<< FLAGS_d_lpr << " plugin" << std::endl; _enabled = true; return netReader.getNetwork(); }

Listing 1: Bereitgestellt in der Beispielanwendung für Sicherheitsbarrierenkameras von Intel im OPENVINO-Toolkit, zeigt dieses Snippet das Designmuster für den Einsatz der Intel Inference Engine C++-Bibliotheks-API zum Einlesen eines Modells und seiner Parameter in die Inferenz-Engine. (Codequelle: Intel)

Um Inferenzen durchzuführen, lädt der Code Daten und ruft die Methode submitRequest auf, die den Inferenzzyklus initiiert und auf das Ergebnis wartet, um anschließend die auf dem Kennzeichen erkannten Zeichen anzuzeigen (Listing 2).

Kopieren if (LPR.enabled()) { // licence plate // expanding a bounding box a bit, better for the license plate recognition result.location.x -= 5; result.location.y -= 5; result.location.width += 10; result.location.height += 10; auto clippedRect = result.location & cv::Rect(0, 0, width, height); cv::Mat Plate = frame(clippedRect); // ----------------------------Run License Plate Recognition LPR.enqueue(Plate); t0 = std::chrono::high_resolution_clock::now(); LPR.submitRequest(); LPR.wait(); t1 = std::chrono::high_resolution_clock::now(); LPRNetworktime += std::chrono::duration_cast<ms>(t1 - t0); LPRInferred++; // ----------------------------Process outputs cv::putText(frame, LPR.GetLicencePlateText(), cv::Point2f(result.location.x, result.location.y + result.location.height + 15), cv::FONT_HERSHEY_COMPLEX_SMALL, 0.8, cv::Scalar(0, 0, 255)); if (FLAGS_r) { std::cout << "License Plate Recognition results:" << LPR.GetLicencePlateText() << std::endl; } } cv::rectangle(frame, result.location, cv::Scalar(0, 0, 255), 2); }

Listing 2: Dieses Snippet aus der Beispielanwendung für Sicherheitsbarrierenkameras von Intel im OPENVINO-Toolkit veranschaulicht das Designmuster für das Laden eines Modells, Durchführen der Inferenz und Bereitstellen der Ergebnisse. (Codequelle: Intel)

Integrierte eingebettete Bildverarbeitungsplattform

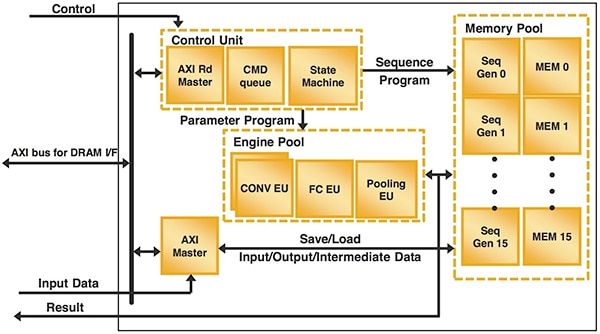

Während bei Intels OPENVINO-Ansatz Plattform-Retargeting im Vordergrund steht, konzentriert sich Lattice mit der SensAI-Plattform strikt auf FPGA-Inferenz. Zu den Merkmalen der SensAI-Plattform zählt, dass sie FPGA-IP für DNN-Architektur bereitstellt, einschließlich CNNs und einer kompakten Architektur, die als binarisiertes neuronales Netzwerk (BNN) bezeichnet wird. Für Embedded-Vision stellt das SensAI-CNN-IP das Framework für eine vollständige Inferenz-Engine bereit, kombiniert Schnittstellen für ein Steuerungssubsystem, Speicher, Eingang und Ausgang mit Ressourcen, die verschiedene Modellschichttypen implementieren, darunter Faltung, BatchNorm-Normalisierung, ReLu-Aktivierung, Pooling und andere (Abbildung 4).

Abbildung 4: Das CNN-IP von Lattice Semiconductor implementiert das komplette Framework für ein Inferenzsystem, indem es spezialisierte Engines und Schnittstellen für Steuerung, Speicher, Eingang und Ausgang implementiert. (Bildquelle: Lattice Semiconductor)

Bei der Implementierung eines CNN-Modells beginnen Entwickler mit der Konfiguration des CNN und nutzen dafür das Konfigurationstool Clarity von Lattice in der Lattice Diamond Designumgebung für ECP5 FPGAs oder Radiant für andere Lattice FPGA-Familien. Hier können Entwickler den Modelltyp (CNN oder BNN), die Anzahl der Faltungsengines (max. acht) und die Größe des internen Speichers (bis zu 16 KB) für jede Schicht oder jeden Blob angeben. Nach der Konfiguration des CNN wird die Designumgebung genutzt, um den Kern als FPGA-Bitstrom zu generieren.

Getrennt importieren Entwickler mit Caffe oder TensorFlow entwickelte, trainierte Modelle in die SensAI-Plattform. Hier konvertiert der Neural Network Compiler von Lattice die trainierten Caffe- oder TensorFlow-Modelle in einen Dateisatz, der die Modellparameter des neuronalen Netzwerks und die Ausführungsbefehlssequenzen enthält. Die SensAI-Plattform bringt die separaten Ausgänge von der Designumgebung und vom Compiler im FPGA zusammen, um ein letztes Inferenzmodell bereitzustellen (Abbildung 5).

Abbildung 5: Die SensAI-Plattform von Lattice Semiconductor kombiniert ihre CNN- und BNN-IP mit dem Neural Network Compiler und ermöglicht so Entwicklern, Caffe- oder TensorFlow-Modelle so zu konvertieren, dass sie als Inferenz-Engines auf Lattice-FPGAs ausgeführt werden können. (Bildquelle: Lattice Semiconductor)

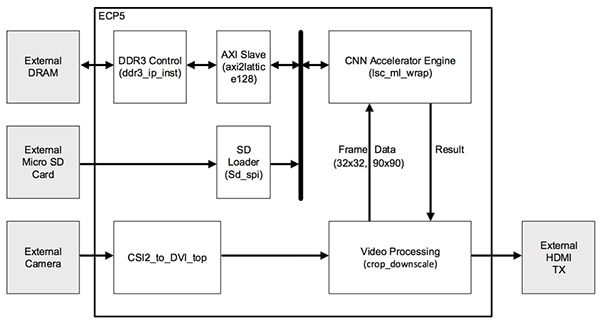

Für eingebettete Bildverarbeitungsanwendungen bietet das Embedded-Vision-Entwicklungskit (EVDK) LF-EVDK1-EVN von Lattice eine Plattform für das Ausführen von CNN-Modell-Inferenzen. Das EVDK bietet eine vollständige Videoplattform in einem Dreiplatinenstapel der Größe 80 x 80 mm, das die Video-Eingangskarte CrossLink von Lattice, eine Prozessorkarte mit einem ECP5-FPGA und eine HDMI-Ausgangskarte beinhaltet. Entwickler können das EVDK als Zielplattform für eine Reihe von CNN-Beispielanwendungen verwenden, die von Lattice erhältlich sind. Zum Beispiel kann das Referenzdesign für das Erkennen von Geschwindigkeits-Verkehrszeichen von Lattice mit dem EVDK verwendet werden, um die Anwendung des SensAI CNN-IP in einer typischen Automobilanwendung zu veranschaulichen (Abbildung 6).

Abbildung 6: Das Referenzdesign für das Erkennen von Geschwindigkeits-Verkehrszeichen von Lattice Semiconductor nutzt die SensAI-Plattform und das Embedded-Vision-Entwicklungskit LF_EVDK1-EVN von Lattice, um eine komplette Inferenzanwendung bereitzustellen, die Entwickler sofort in Betrieb nehmen oder detailliert untersuchen können. (Bildquelle: Lattice Semiconductor)

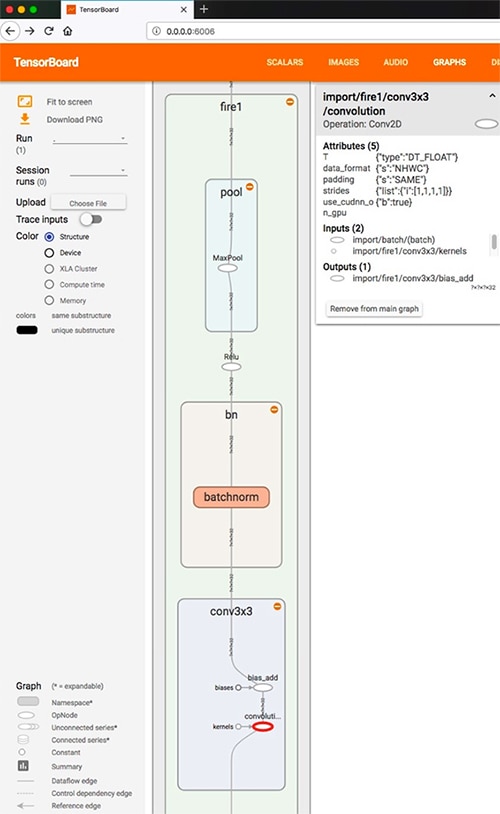

Die Projektdateien für diese Beispielanwendung beinhalten den kompletten Dateiensatz, angefangen bei den Modellen, die in Caffe-caffemodel- und TensorFlow-pb-Formaten bereitgestellt werden. Dadurch können Entwickler die Details dieser Modelle erforschen. Mit dem TensorFlow-Programm import_pb_to_tensorboard.py beispielsweise können Entwickler das von Lattice bereitgestellte pb-Modell importieren, um die Details des in dieser Beispielanwendung verwendeten CNN zu studieren (Abbildung 7). In diesem Fall ist das bereitgestellte Modell eine Abfolge von vier "Fire"-Modulen, wovon ein jedes Folgendes umfasst:

- Eine Conv2D-Schicht, die die 3 x 3 Faltung durchführt, um Merkmale aus dem Eingangsstrom zu extrahieren

- Eine Aktivierungsschicht, die eine BatchNorm-Normalisierung durchführt, gefolgt von der Aktivierung einer gleichgerichteten linearen Einheit (Rectified Linear Unit – ReLU)

- Eine MaxPool-Pooling-Schicht, die den Ausgang der vorherigen Schicht abfragt

Abbildung 7: Die Beispielanwendung für das Erkennen von Geschwindigkeits-Verkehrszeichen von Lattice enthält TensorFlow-pb-Modelle, die Entwickler zur genaueren Erforschung in TensorBoard importieren können. Hinweis: In diesem Diagramm strömen Daten aufwärts durch die Schichten. (Bildquelle: DigiKey)

Entwickler können den oben beschriebenen Modell-Prozessablauf durcharbeiten und die SensAI-Plattform zum Generieren der Modelldateien verwenden. Alternativ können Entwickler direkt in die Bereitstellung springen und dazu die bereitgestellten Dateien verwenden. In beiden Fällen werden die Dateien via eine über einen Adapter angeschlossene MicroSD-Karte in das EVDK geladen.

Im Betrieb bietet die Kamera auf dem EVDK einen Videostrom zum ECP5 FPGA, wo das konfigurierte CNN-Beschleuniger-IP Befehlssequenzen zur Durchführung der Inferenz ausführt. Wie bei jeder Inferenz-Engine erzeugt jeder Ausgangskanal ein Ergebnis, das die Wahrscheinlichkeit liefert, dass das mit dem Ausgangskanal verknüpfte Label das korrigierte Label für das Eingangsbild ist. In diesem Fall wurde das Modell mit Bildern von Verkehrszeichen zur Geschwindigkeitsbegrenzung für 25, 30, 35, 40, 45, 50, 55, 60 und 65 Meilen pro Stunde trainiert. Wenn das Modell ein Verkehrszeichen in seinem Eingangsfeld entdeckt, zeigt es folglich die Wahrscheinlichkeit an, dass das erkannte Verkehrszeichen einer Geschwindigkeitsbegrenzung auf 25, 30, 35, 40, 45, 50, 55, 60 oder 65 Meilen pro Stunde entspricht (Abbildung 8).

Abbildung 8: Ausgeführt auf dem Lattice EVDK, führt die Demo der Geschwindigkeits-Verkehrszeichenerkennung von Lattice eine Inferenz des Video-Eingangsstroms durch und generiert Ausgangswerte, die die Wahrscheinlichkeit anzeigen, dass das erfasste Bild einem Label entspricht, das mit dem jeweiligen Ausgang verknüpft ist. In diesem Fall zeigt es, dass das Verkehrszeichen zur Geschwindigkeitsbegrenzung am wahrscheinlichsten 25 Meilen pro Stunde vorgibt. (Bildquelle: Lattice Semiconductor)

Fazit

Beim Einsatz von maschinellem Lernen in eingebetteten Bildverarbeitungsanwendungen waren Entwickler bis jetzt eingeschränkt hinsichtlich der Möglichkeit, die erforderlichen Leistungsniveaus für die Verwendung verfügbarer Hardware-Plattformen zu erzielen. Mit dem Aufkommen von High-Performance-FPGAs können Entwickler jedoch Inferenz-Engines schaffen, die der Leistung von GPUs nahe kommen können. Mit ML-FPGA-Plattformen für eingebettete Bildverarbeitung können sich Entwickler auf ihre spezifischen Anforderungen konzentrieren, Standard-Frameworks für maschinelles Lernen verwenden, um Modelle zu trainieren, und sich darauf verlassen, dass die FPGA-Plattform High-Performance-Inferenz liefert.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.