Mit Flashless-Mikrocontrollern erhöhen Sie die Leistung bei sinkenden Systemkosten

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-08-22

IoT-Netzwerken (Internet der Dinge) werden heute zunehmend komplexere Aufgaben abverlangt. Im Zuge dessen stiegen auch die Speicheranforderungen von IoT-Endpunkten, vor allem bei Endpunkten, die heute Daten auf einem sehr viel höheren Niveau verarbeiten müssen. Der Flash-Speicher von On-Chip-Mikrocontrollern ist auf rund 1 Megabit (Mbit) limitiert. Viele High-End-IoT-Endpunkte benötigen allerdings ein Vielfaches dessen.

Die konventionelle Lösung für dieses Problem bestand bisher darin, den Programmspeicher des Mikrocontrollers mit einem externen Flash-Chip zu erweitern. Bei einem Speicherbedarf von 8 Mbit oder mehr befindet sich dann jedoch der größte Teil des Programmspeichers nicht mehr auf dem Chip.

In vielen Fällen sind Entwickler daher besser beraten, ganz auf On-Chip-Flash zu verzichten und stattdessen mit einem Mikrocontroller ohne Flash-Speicher (oder ROM) in Kombination mit einem externen Hochgeschwindigkeits-Oktal-XiP-Flash-Chip (XiP: eXecute-in-place) zu arbeiten. Das senkt erheblich die Kosten des Mikrocontrollers und macht das System zukunftssicher, weil es eine größere Skalierbarkeit bietet. Bedenken hinsichtlich der Speicherzugriffszeiten dürften ausgeräumt sein, seit es die extrem schnellen Oktal-Speicherschnittstellen gibt.

Dieser Artikel befasst sich mit ROMless-Mikrocontrollern und externen Speichern sowie ihrer Entwicklung hin zu einer brauchbaren Alternative für IoT-Endpunkte und Embedded-Systeme, die viel Programmspeicher benötigen. Anschließend wird gezeigt, wie das Konzept mit Hilfe von ROMless-Mikrocontrollern von NXP Semiconductors und einem Oktal-SPI-XiP-Flash-Chip von Adesto Technologies angewendet werden kann.

Speichererweiterung an den Endpunkten des IoT

Die meisten IoT-Endpunkte mit niedriger bis mittlerer Leistung nutzen für die Verwaltung des Endpunktes einen Mikrocontroller, wobei die Firmware auf dem On-Chip-Flash gespeichert ist. Durch Hinzukommen von zusätzlichem Anwendungscode, Stacks für die drahtlose IP-Kommunikation und verbessertem Sicherheitscode nimmt die Firmware an Umfang zu. Die Code-Erweiterung kann während der Entwicklung und in Folge von Updates im laufenden Betrieb auftreten.

Einige dieser IoT-Endpunkte müssen jetzt mehr Datenverarbeitungsfunktionen ausführen. Statt Roh- oder teilweise verarbeitete Sensordaten zur Verarbeitung über das Netzwerk an einen Zentralrechner zu schicken, führen diese IoT-Endpunkte komplexere Aufgaben wie beispielsweise Sensor-Fusionsalgorithmen, Interpolation von Daten, Muster- oder Bilderkennung und zunehmend komplexere KI-Datenverarbeitung aus.

Weil der Zentralrechner dadurch statt aller Bytes der Sensor-Rohdaten nur das Ergebnis der lokalen Verarbeitung des IoT-Knotens empfängt, kann das Verkehrsaufkommen im Funknetz sinken. Und da der HF-Sender in einem IoT-Endpunkt der größte Verbraucher sein kann, macht sich die Randknotenverarbeitung (Edge Computing) bei batteriebetriebenen Endpunkten häufig mit einer Verlängerung der Batterielebensdauer bezahlt.

Bei Systemen, die vor Ort aktualisiert werden müssen, ergeben sich weitere Herausforderungen, was den Speicher angeht. Herkömmliche Systeme benötigen für die Durchführung solcher Updates mindestens das Doppelte des geschätzten Programmspeicherplatzes. Das liegt daran, dass sowohl der vorhandene Programmspeicher als auch die Größe von OTA-Updates (Over-the-Air) gehandhabt werden muss. Einige Systeme können das Dreifache des geschätzten Programmspeicherplatzes benötigen, wobei der zusätzliche Speicher werkseitig einem schreibgeschützten Firmware-Image zugewiesen wird. Bei bestimmten Arten von Systemfehlern, darunter die Erkennung von Hackerangriffen oder eines beschädigten Firmware-Images, kann das System das ursprüngliche werkseitige Firmware-Image laden, um das System wiederherzustellen.

Bei bestimmten Anwendungen kann diese Speichererweiterung schnell die 1-Mbit-Grenze für eingebettete Flash-Speicher überschreiten, was eine externe Speichererweiterung erforderlich macht. Traditionell bestand die Lösung darin, das System um einen externen parallelen Flash-Speicherchip zu erweitern. Dies hat jedoch den Nachteil, dass circa 36 externe Pins am Mikrocontroller belegt werden – Pins, die sonst für Anwendungseingänge und -ausgänge genutzt werden könnten. Zudem wird dadurch unnötiger Platz auf der Platine belegt, und es steigt die Wahrscheinlichkeit von elektromagnetischen Störungen (EMI) von der Platine.

Erweiterung des Programmspeichers per SPI

Außer mit einem parallelen Bus kann der Programmspeicher auch über die SPI-Schnittstelle (Serial Peripheral Interface) erweitert werden. Die herkömmliche SPI nutzt nur eine Datenleitung für Halbduplex-Einzelbit-Übertragungen, wurde aber im Laufe der Jahre so erweitert, dass auch Dual- und Quad-Datenleitungen unterstützt werden. Das führte zu einer entsprechenden Erhöhung des Datendurchsatzes. Dieser stieg bis zu einem Punkt, an dem es sich anbot, einen externen SPI-Flash-Chip mit großer Kapazität anzubinden.

Für Programmspeicher-Anwendungen nutzt eine herkömmliche Dual- oder Quad-SPI eine Shadow-Flash-Konfiguration, bei der der externe Flash-Datenspeicher in einen eingebetteten statischen Direktzugriffsspeicher (SRAM) kopiert wird, dessen Abbild in den Programmspeicherbereich übertragen wird. Dies hat zwar den Vorteil, dass der Programmspeicher auf einfache Weise erweitert werden kann – unter Verbesserung der Ausführungsgeschwindigkeit, wenn schneller SRAM knapp wird –, hat jedoch auch erhebliche Nachteile. Weil die Menge des internen SRAM begrenzt ist, wird im Paged-Modus auf den Speicher zugegriffen, weil der Flash-Speicher bei Bedarf in den internen SRAM umgelegt wird. Dieser Engpass lässt sich durch mehr SRAM auf dem Chip verringern. Weil SRAM jedoch einer der teuersten Blöcke auf jedem Halbleiter ist, hat dies den Nachteil, dass die Kosten des Mikrocontrollers stark steigen.

Eine noch gar nicht so alte Weiterentwicklung von SPI war XiP. Mit SPI XiP kann die CPU des Mikrocontrollers den Firmware-Code direkt aus dem externen SPI-Flash ausführen. Die Programmausführungsgeschwindigkeit lässt sich durch Ergänzung der SPI XiP-Schnittstelle um einen Cache erheblich verbessern.

Die Popularität von SPI XiP führte zur kürzlich erfolgten Erweiterung der Schnittstelle um acht Datenleitungen. Diese oktale SPI-XiP-Schnittstelle brachte den Durchsatz an einen Punkt, an dem er viel höher als bei dem auf dem Chip verfügbaren Flash-Speicher ist – mehr als 100 Mbit/s.

Die SPI-Speicherrevolution

Dies führte zu einer kuriosen Entwicklung, deren Ursprünge bis zu 30 Jahre zurückreichen. Stellen wir uns einmal ein System vor, das über 1 Mbit Flash auf dem Chip und 32 Mbit externen Programmspeicher-Flash verfügt, auf den über eine oktale SPI-XiP-Schnittstelle zugegriffen wird. Der On-Chip-Programmspeicher ist so klein, dass sich die Frage stellt: Kann dieser On-Chip-Mikrocontroller-Flash sogar ganz entfallen, ohne der Vorteil der günstigen Kosten einzubüßen?

Lange ging man davon aus, dass ein System im mittleren Bereich mit einem Flash-Mikrocontroller immer kostengünstiger als ein System mit Flashless-Mikrocontroller und externem Flash-Chip ist. Das hat sich erst vor kurzem geändert.

Wenn der On-Chip-Flash-Speicher entfällt, sinken dadurch natürlich die Kosten des Mikrocontrollers. Bei genauerem Hinschauen zeigt sich jedoch, dass auch die prozesstechnischen Features, die ausschließlich für Flash genutzt werden, entfallen können, wenn der Flash nicht mehr benötigt wird. Das senkt die Kosten des Herstellungsprozesses und damit die Kosten des Mikrocontrollers erheblich. Dadurch erlebt ein System eine Renaissance, das vor rund 30 Jahren als „ROMless“-Mikrocontroller bezeichnet wurde. Heute nennen wir es Flashless.

(Neu-)einführung in Flashless-Mikrocontroller

Ein Hochleistungs-Mikrocontroller der die Geschwindigkeit von Flash-Speicher nutzen kann, ist der (Flashless-) MIMXRT1052DVL6B (RT1052) von NXP Semiconductors. Der RT1052 ist Teil der Prozessorfamilie i.MX RT1050 von NXP. Er basiert auf einem mit 600 MHz getakteten Arm®-Cortex®-M7 mit 32 KByte Instruction-Cache und 32 KByte Daten-Cache. Die Taktrate von 600 MHz wird durch Wegfall des Flash und die Nutzung einer schnellen CMOS-Prozesstechnologie erreicht, die nicht durch den internen Flash-Speicher beschränkt ist. Der RT1052 verfügt über einen großen SRAM-Speicher (512 KB), der für die Verwendung als Programm- oder Datenspeicher partitioniert werden kann.

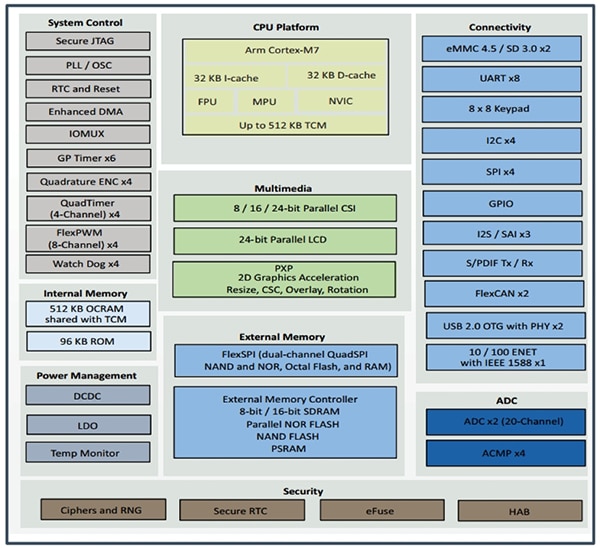

Der Mikrocontroller verfügt über ein breites Spektrum an High-End-Peripheriekomponenten, darunter eine LCD-Schnittstelle, eine Digitalkamera-Sensor-Schnittstelle (CSI) und eine Pixel Processing Pipeline (PXP) für die Unterstützung von High-End-Kameras, eine SPDIF-Schnittstelle für digitales Audio, zwei USB-OTG-Schnittstellen und zwei eMMC-/SD-Flash-Kartenschnittstellen, zwei 20-Kanal-AD-Wandler (ADC) und ein Verschlüsselungsmodul. Eine vollständige Liste der Peripheriekomponenten finden Sie im Blockdiagramm (Abbildung 1).

Abbildung 1: Der NXP RT1052 bietet ein breites Spektrum an Peripheriekomponenten, darunter eine serielle SPI-XiP-Schnittstelle sowie Unterstützung für die Datenverschlüsselung. (Bildquelle: NXP)

Abbildung 1: Der NXP RT1052 bietet ein breites Spektrum an Peripheriekomponenten, darunter eine serielle SPI-XiP-Schnittstelle sowie Unterstützung für die Datenverschlüsselung. (Bildquelle: NXP)

Eine weitere Option ist der NXP MIMXRT1051DVL6B (RT1051). Er hat dieselbe Ausstattung wie der RT1052, allerdings ohne LCD-Schnittstelle, CSI und PXP.

Dafür hat der RT1052 eine FlexSPI-Schnittstelle, über die sich unter Verwendung einer Dual-, Quad- oder Oktal-SPI-XiP-Flash-Schnittstelle Code ausführen lässt. Zur Erhöhung der Sicherheit der Firmware unterstützt der Mikrocontroller verschlüsselten Programmspeicher über SPI XiP. Ein gutes Beispiel dafür ist der ATXP032-CCUE-T von Adesto Technologies.

Moderner XiP-Flash-Betrieb

Der ATXP032-CCUE-T von Adesto ist ein 32-Mbit-Oktal-Flash-Chip, der Datentransfers mit bis zu 266 MByte pro Sekunde in Oktal-Dual-Transferratenmodus (DTR) unterstützt – viel mehr als ein On-Chip-Mikrocontroller-Flash-Speicher. Er benötigt eine einfache 1,8V-Spannungsversorgung und weist im Oktal-Modus einen typischen Standby-Strom von 35 Mikroampere (µA) auf. Er unterstützt einen maximalen SPI-Takt von 133 MHz.

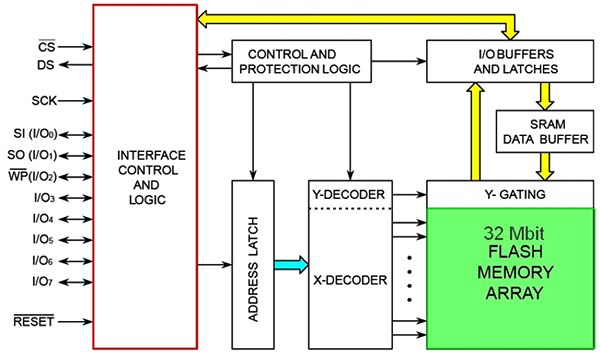

Abbildung 2: Der Flash-Speicher ATXP032-CCUE-T von Adesto nutzt eine Oktal-SPI, I/O0 bis I/O7, für den Anschluss an einen Mikrocontroller. Ein SRAM-Schreibdatenpuffer verbessert die Leistung von Schreibvorgängen auf Flash. (Bildquelle: Adesto Technologies)

Abbildung 2: Der Flash-Speicher ATXP032-CCUE-T von Adesto nutzt eine Oktal-SPI, I/O0 bis I/O7, für den Anschluss an einen Mikrocontroller. Ein SRAM-Schreibdatenpuffer verbessert die Leistung von Schreibvorgängen auf Flash. (Bildquelle: Adesto Technologies)

Bei einem aktiven Flash-Lesevorgang liegt die Stromaufnahme des ATXP32 bei 142 µA/MHz plus 1 Milliampere (mA) Overhead (typisch). Bei seiner höchsten SPI-Taktrate von 133 MHz im Oktal-Modus nimmt er lediglich 19,9 mA auf.

Der ATXP032-CCUE-T unterstützt zudem die Standard-SPI-Modi 0 und 3 sowie den Quad-SPI-Modus. Ein 256-Byte-Sicherheitsregister verfügt über eine werkseitig programmierte eindeutige 128-Byte-Kennung sowie 128 Byte OTP-Speicher (einmalig programmierbar), in dem Geräteinformationen wie eine Ethernet-MAC-Adresse (Media Access Control) oder ein Sicherheitsschlüssel gespeichert werden können.

Bemerkenswert ist die Speicheranordnung des ATXP032-CCUE-T. Sie ist in vier Bänke mit jeweils 8 Mbit aufgeteilt. Die interne Logik ist so konfiguriert, dass ein Host-Mikrocontroller Code aus einer Bank ausführen kann, während gleichzeitig eine andere programmiert oder gelöscht wird. Der Betrieb ist für den Host-Mikrocontroller transparent und erfordert keine speziellen Konfigurationseinstellungen.

Zudem verfügt der ATXP032-CCUE-T über drei Status- und Steuerregister für das Konfigurieren der Betriebsparameter des Geräts, z. B. Energiesparmodus, Aktivieren oder Deaktivieren des DTR-Modus und Festlegen des Standard-, Quad- oder Oktal-SPI-Modus (Standard-SPI ist die Vorgabe). Aus den Statusregistern lässt sich Folgendes auslesen: der Status eines Programmier- oder Löschvorgangs, der Energiesparmodus und, ob einer der Speicher schreibgeschützt ist.

Kombinieren von Flashless-Mikrocontrollern und externem XiP

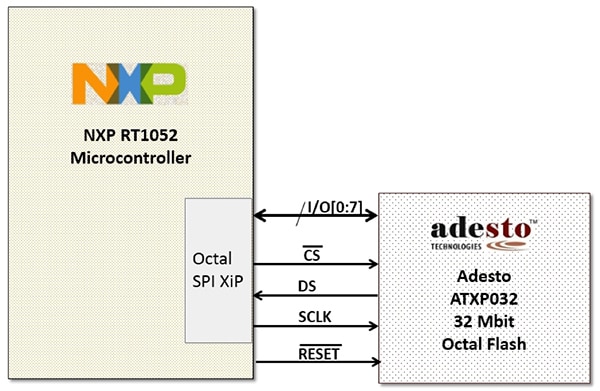

RT1052 und ATXP032-CCUE-T lassen sich unkompliziert kombinieren (Abbildung 3). Beim Einschalten führt der RT1052 Code aus dem On-Chip-Boot-ROM mit seinen 96 KByte aus. Der Boot-ROM liest den Status von 14 Boot-Modus-Konfigurations-Pins, die bestimmen, welche der vielen externen Speicherschnittstellen des RT1052 für den Programmspeicher zu verwenden sind. Zu den Optionen gehören eine externe eMMC-Karte, eine Micro-SD-Karte, eine herkömmliche externe Parallelschnittstelle oder der SPI XiP (in diesem Fall der ATXP032-CCUE-T von Adesto).

Abbildung 3: Der Flashless-Mikrocontroller NXP RT1052 hat eine Oktal-SPI-XiP-Schnittstelle für die einfache Verbindung mit dem ATXP032-CCUE-T von Adesto. Der Betrieb der Oktal-SPI-XiP-Schnittstelle ist für den Arm-Kern transparent. (Bildquelle: DigiKey)

Abbildung 3: Der Flashless-Mikrocontroller NXP RT1052 hat eine Oktal-SPI-XiP-Schnittstelle für die einfache Verbindung mit dem ATXP032-CCUE-T von Adesto. Der Betrieb der Oktal-SPI-XiP-Schnittstelle ist für den Arm-Kern transparent. (Bildquelle: DigiKey)

Die Boot-Optionen des RT1052 schließen auch das Herunterladen von Code vom USB-OTG oder UART zur Ausführung auf dem SRAM ein. Die Boot-Modus-Optionen können statt mit den Boot-Modus-Konfigurationspins auch während der Herstellung durch Auslösen interner Sicherungen im RT1052 festgelegt werden. Sobald die Oktal-SPI-XiP-Schnittstelle vom Boot-ROM des RT1052 für die Ausführung des Programmspeichers aktiviert wurde, wird das Programm ausgeführt. Der Arm-Kern führt dann die Firmware des ATXP032-CCUE-T von Adesto auf dieselbe Weise wie ein externes paralleles Flash-Gerät oder interner Flash-Speicher aus.

Aufgrund der dabei auftretenden hohen Geschwindigkeiten bei der Datenübertragung sollte der oktale serielle Flash auf der Platine möglichst nahe am Oktal-SPI-XiP-Port des Mikrocontrollers positioniert werden. Zur Vermeidung von Interferenzen sollte keine der Leiterplattenbahnen länger als 120 Millimeter sein. Das Taktsignal sollte in einem Abstand von mindestens der dreifachen Breite der Leiterbahnen auf der Platine platziert sein, um Interferenzen zu vermeiden. Zur Vermeidung von Versatz sollten die bidirektionalen Datensignale I/O [0:7] alle innerhalb von 10 mm zueinander angeordnet sein.

Fazit

Aufgrund der Tendenz zu zunehmend komplexeren Datenverarbeitungsvorgängen am Rand des IoT und der Notwendigkeit von OTA-Updates und den damit einhergehenden Anforderungen an die Skalierbarkeit des Speichers haben IoT-Endpunkte einen steigenden Speicherbedarf. Ab einem bestimmten Punkt kommt für die Entwickler dieser Endgeräte dabei die Option in Frage, einen Flashless-Mikrocontroller einzusetzen.

Wie beschrieben, bieten Fortschritte bei Flashless-Mikrocontrollern, Highspeed-Schnittstellen und Oktal-SPI-XiP-Flash-Chips Entwicklern die Möglichkeit, leistungsfähige, kostengünstige IoT-Endpunkte oder Embedded-Systeme zu entwickeln, statt auf herkömmliche Flash-basierte Mikrocontroller-Konzepte zurückzugreifen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.