Die Grundlagen von direkten digitalen Synthesizern (DDS), ihre Wahl und ihre Verwendung

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-03-20

Mit der Verbreitung von drahtlosen Geräten werden von den Entwicklern immer komplexere und variable Wellenformen eingesetzt, um die Anforderungen in Bezug auf Datenraten, Störungsunterdrückung, Kosten, Abmessungen und niedrigem Energieverbrauch zu erfüllen. Diese Wellenformen erfordern stabile HF-Quellen, die bei Bedarf abgestimmt werden können und bezüglich Frequenz und Phase flexibel sind. Gleichzeitig müssen die Quellen ein Signal von hohem Reinheitsgrad liefern. Die Lösung für dieses Anforderungsspektrum sind direkte digitale Synthesizer (DDS).

DDS generieren analoge Wellenformen mithilfe von digitalen Methoden und profitieren so von der Programmierbarkeit der Digitaltechnik, einem höheren Integrationsgrad und geringeren Kosten. Darüber hinaus erlauben DDS fast augenblickliche Änderungen von Frequenz oder Phase. Dies macht sie zu der bevorzugten Quelle für komplexe digitale Modulationstechniken wie Frequenzumtastung (Frequency Shift Keying, FSK) und Spreizspektrum sowie für den Einsatz von Techniken zur Störungsunterdrückung, z. B. von Frequenzsprungverfahren. Daher werden die herkömmlichen Phasenregelkreise (Phase Locked Loops, PLLs) und andere analoge Quellen zunehmend durch DDS-ICs ersetzt oder erweitert, die eine hohe Stabilität und Signalreinheit bieten.

In diesem Artikel werden die Grundlagen der DDS-Technologie und die Spezifizierung von DDS-ICs behandelt. Dann werden einige geeignete DDS-IC-Lösungen vorgestellt und ihr effektiver Einsatz vorgeführt.

Die Funktionsweise der direkten digitalen Synthese

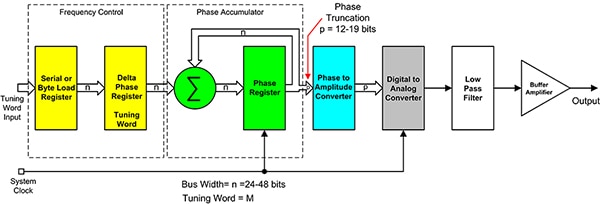

Die digitale Synthese beruht auf einem Phasenakkumulator, der eine Folge von digitalen Zuständen generiert, deren Werte linear ansteigen und so eine numerische Rampe bilden. Dieses Signal wird periodisch gemacht und stellt die momentane Phase der Ausgangs-Wellenform von 0 bis 2 π (rad) dar. Dies stellt die digitalen Eingabe in eine Lookup-Tabelle dar, die die numerische Rampe in eine Sinuswelle konvertiert (Abbildung 1). Sinuswellen sind zwar die gebräuchlichsten Ausgangs-Wellenformen eines DDS, es können aber ebenso leicht Rampen, Dreieck- und Rechteckwellen generiert werden.

Abbildung 1: Ein direkter digitaler Synthesizer beruht auf einem Phasenakkumulator, der die momentane Phase einer Wellenform generiert. Eine Lookup-Tabelle liefert die Konvertierung von der Phase zur Amplitude. Das Ergebnis wird dann durch einen Digital-Analog-Wandler geschickt, der nach Filterung die gewünschte analoge Ausgabe liefert. (Bildquelle: DigiKey)

Die Ausgabe der Phase-Amplitude-Lookup-Tabelle wird durch einen Digital/Analog-Wandler (DAC) geschickt und in eine analoge Wellenform konvertiert, die in der Regel eine Sinusform hat. Da es sich bei der Eingabe in den DAC um eine Folge von gesampelten Werten handelt, enthält die Ausgabe Quantisierungsschritte. Diese Schritte produzieren im Frequenzbereich unerwünschte spektrale Abbilder bei Vielfachen der Abtastrate. Ein Tiefpass hinter dem DAC unterdrückt diese unerwünschten Spektralantworten.

Der Phasenakkumulator

Der Phasenakkumulator ist ein Modulo-N-Zähler mit 2N digitalen Zuständen, die bei jedem Impuls des Systemtakts inkrementiert werden. Die Größe der Inkrementierung hängt vom Wert des Abstimmungsworts M ab, das auf die Addierstufe des Akkumulators angewendet wird. Das Abstimmungswort legt die Schrittweite des Zählerinkrements fest. Dadurch wird die Frequenz der Ausgangswellenform festgelegt.

Der Phasenakkumulator hat normalerweise 24 bis 48 Bit. Bei 24 Bit gibt es 224, d.h. 16.777.216 mögliche Zustände. Diese Zahl repräsentiert die Anzahl der Phasenwerte zwischen 0 und 2 Pi (rad), d.h. das erzielbare Phaseninkrement. Die Auflösung eines 24-Bit-Phasenakkumulators beträgt 3,74 E-7 (rad). Je größer der Phasenakkumulator ist, desto feiner ist das Phaseninkrement.

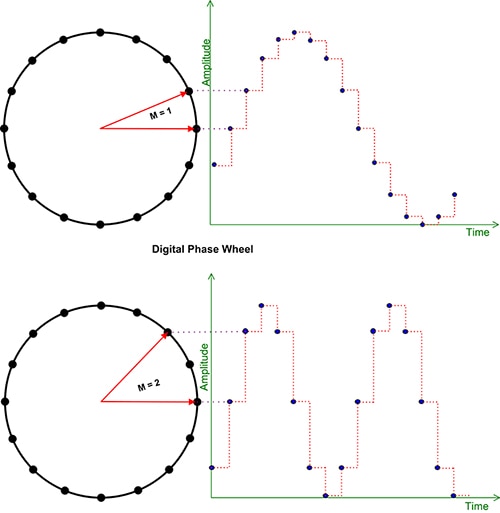

Eine Möglichkeit, die Funktion des Phasenakkumulators zu visualisieren, besteht darin, den Phasenakkumulator als Phasenrad zu betrachten (Abbildung 2).

Abbildung 2: Eine vereinfachte Darstellung der Funktion eines Phasenakkumulators mit 16 Zuständen mit einem Phasenrad zur Visualisierung der Auswirkung des Abstimmungsworts auf die Ausgangsfrequenz des DDS. (Bildquelle: DigiKey)

Die Zustände des Akkumulators wiederholen sich periodisch und sind hier als Kreis dargestellt. Die Punkte auf dem Kreis stellen die Phasenzustände des Akkumulators dar. In diesem Fall hat der Akkumulator der Einfachheit halber 16 Zustände. Wenn das Abstimmungswort wie im Diagramm oben den Wert 1 hat, beträgt das Inkrement pro Schritt bei jedem Takt 1 und alle Zustände werden innerhalb einer vollen Periode angenommen.

Rechts vom Phasenrad ist die analoge Ausgabe für jeden Zustand projiziert. Da es sich um ein quantisiertes Bauelement handelt, behält der analoge Ausgang seinen aktuellen Status so lange, bis der Takt das Phasenrad zum nächsten Zustand bewegt. Die ausgegebene Wellenform besteht aus einem einzelnen Zyklus der quantisierten Sinuswelle mit 16 Werten.

Im unteren Diagramm hat das Abstimmungswort den Wert 2. Bei dieser Einstellung wird jeder zweite Wert des Phasenrads angenommen. Die analoge Ausgabe besteht jetzt aus zwei Zyklen mit je acht Amplituden, also mit insgesamt 16 Zuständen. Da das Abstimmungswort den Wert 2 hat, ist die Ausgangsfrequenz doppelt so hoch wie vorher.

Die Ausgangsfrequenz des DDS wird durch das Abstimmungswort festgelegt und wächst proportional zu diesem. Die Abtastrate ist auf die Taktfrequenz des Systems festgelegt und das Zeitintervall zwischen den Ausgangssamples ist konstant. Die Ausgangsfrequenz hängt vom Wert des Abstimmungsworts ab. Wenn also das Abstimmungswort größer wird, enthält ein Ausgabezyklus weniger Schritte, wodurch sich die Frequenz erhöht. Das Abstimmungswort kann erhöht werden, bis ein Zyklus nur noch aus zwei Samples besteht, wodurch die Ausgabe des DDS seine Nyquist-Frequenz, also die halbe Taktfrequenz des Systems, erreicht. Ein DDS ist bauartbedingt generell auf eine Ausgangsfrequenz begrenzt, die kleiner als die Nyquist-Grenze ist.

Die Ausgangsfrequenz des DDS hängt außer von der Taktfrequenz des Systems vom Wert des Abstimmungsworts und der Länge des Akkumulators ab. Dies wird durch Gleichung 1 ausgedrückt:

![]() Gleichung 1

Gleichung 1

Dabei gilt:

fout ist die Ausgangsfrequenz des DDS

M ist der Wert des Abstimmungsworts

fc ist die Taktfrequenz des Systems

N ist die Länge des Phasenakkumulators

Die Ausgabe des Phasenakkumulators, die jeweils die augenblickliche Phase der Ausgangswellenform darstellt, wird an den Amplitudenwandler übergeben. Der Phasen-Amplituden-Wandler gibt ein digitales Wort aus, dessen Wert der Amplitude der Sinuswelle der Eingangsphase entspricht.

Beachten Sie, dass die Anzahl der Bits, die in den Phasen-Amplituden-Wandler eingehen, geringer als die des Phasenakkumulators ist. Dies wird als Abschneiden der Phase (phase truncation) bezeichnet und soll den Umfang und den Stromverbrauch der digitalen Stufen hinter dem Phasenakkumulator reduzieren. Dies führt zu vereinzelten störenden Spektralkomponenten, die aber durch sorgfältige Auslegung des Designs minimiert werden können.

Der Grund für den Tiefpass am Ausgang

Die Wellenformen in Abbildung 2 sind wegen ihrer Treppenform reich an Oberwellen. Daher ist zum Entfernen dieser Oberwellen und anderer störender Frequenzantworten, die auf Vorgängen innerhalb des DDS beruhen, ein Tiefpass erforderlich.

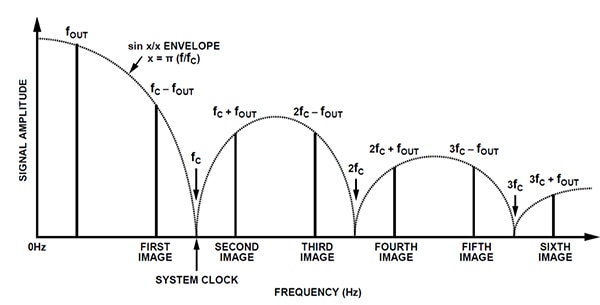

Abbildung 3 zeigt als Beispiel das DDS-Ausgabespektrum eines Bauelements mit Taktfrequenz fc mit einer Ausgangsfrequenz, die kleiner als fc/2 ist. Das Ausgabespektrum zeigt die Ausgabe-Spektrallinie fout mit ihren Bildfrequenzen über und unter der Taktfrequenz sowie alle Oberwellen bis zur dritten und darüber hinaus.

Abbildung 3: Spektralansicht eines DDS mit Systemtaktfrequenz fc und Ausgangsfrequenz fout mit den Komponenten der Ausgangsfrequenz bis zu dritten Oberwelle der Taktfrequenz. (Bildquelle: Analog Devices)

Der Ausgangsfrequenzbereich des DDS reicht von 0 Hz bis zur Nyquist-Grenze bei fc/2. Die Form der Funktion sin(x)/x beruht auf dem quantifizierten Signal im Zeitbereich, siehe Abbildung 2. Die Nullstellen der Funktion sin(x)/x liegen bei der Taktfrequenz und ihren Oberwellen. Es können Korrekturen an der Amplitude angebracht werden, um die sin(x)/x-Form aufzuheben oder um die Gleichförmigkeit der Amplitude über den Ausgangsbereich zu verbessern.

Es wird ein Tiefpass mit einer scharfen Abtrennung oberhalb des Frequenzbereichs des DDS eingesetzt, um die Spektralkomponenten über der Nyquist-Frequenz signifikant zu reduzieren. Wenn der Frequenzbereich des DDS bis zur Nyquist-Frequenz ausgeweitet würde, müsste der Filter eine unendlich steile Flanke besitzen, um die untere Bildfrequenz der Taktfrequenz auszufiltern, die die Nyquist-Frequenz überlappen würde. Unter anderem aus diesem Grund wird die Frequenz eines DDS selten bis zur Nyquist-Frequenz ausgeweitet.

Die Entwicklung mit handelsüblichen DDS-ICs

Bei der Wahl und bei der Verwendung eines DDS ist viel zu beachten. Zunächst sind die benötigte Funktionalität für die Anwendungen zu berücksichtigen: der erforderliche Frequenzbereich, der Amplituden- und Offset-Bereich, die Form der Welle, die Auflösung und die Modulationsfähigkeiten. Die Reinheit des Signals ist ein grundlegender Faktor bei der Wahl einer Signalquelle. SFDR (Spurious Free Dynamic Range, Störungsfreier dynamischer Bereich), THD (Total Harmonic Distortion, Gesamtklirrfaktor) und Phasenrauschen sind wichtige Spezifikationen. Dazu gehört auch der Energieverbrauch, insbesondere bei Mobilanwendungen.

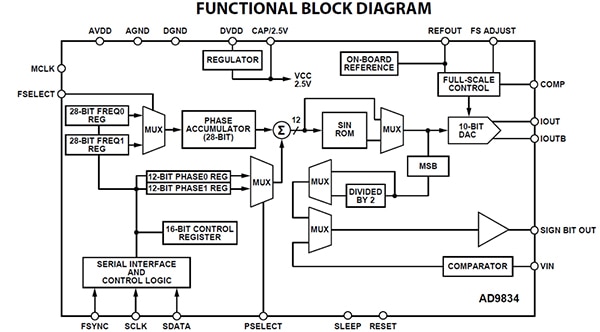

Ein gutes Beispiel für einen DDS mit geringem Energieverbrauch ist der AD9834BRUZ-REEL7 von Analog Devices (Abbildung 4). Der Baustein wird über eine serielle Drei-Draht-Schnittstelle gesteuert, benötigt eine 3V-Stromversorgung und verbraucht nur 20 mW. Er kann Sinus-, Sägezahn- und Rechteckwellen ausgeben. Die maximale Taktfrequenz (am digitalen Takteingang MCLK in der Abbildung) liegt bei 50 MHz. Wie oben anlässlich des Begriffs „Nyquist-Frequenz“ besprochen, bedeutet diese Taktfrequenz, dass Wellenformen mit bis zu 25 MHz ausgegeben werden können.

Abbildung 4: Das interne Funktionsdiagramm des energiesparenden DDS AD9834 von Analog Devices. Der Baustein benötigt eine 3V-Stromversorgung und verbraucht 20 mW. Er kann Sinus-, Sägezahn- und Rechteckwellen mit bis zu 25 MHz ausgeben. (Bildquelle: Analog Devices)

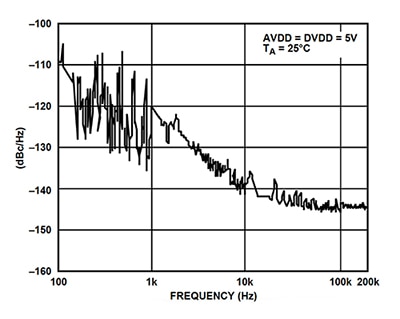

Der Phasenakkumulator hat eine Länge von 28 Bit. Dies liefert eine Auflösung von 0,186 Hz im Frequenzbereich bei einer Taktfrequenz von 50 MHz. Das Phasenrauschen hängt auch von der Qualität des MCLK-Eingangs ab und wird hier als Funktion des Versatzes bezüglich des Trägersignals dargestellt (Abbildung 5). Im Fall des AD9834 beträgt das Phasenrauschen -120 dBc/Hz bei einem Versatz von 1 kHz bezüglich der Trägerfrequenz bei FOUT = 2 MHz und 50 MHz am MCLK-Eingang.

Abbildung 5: Das Phasenrauschen hängt von der MCLK-Qualität ab und beträgt hier -120 dBc/Hz bei einem Versatz von 1 kHz bezüglich der Trägerfrequenz bei FOUT = 2 MHz und 50 MHz am MCLK-Eingang. (Bildquelle: Analog Devices)

Der integrierte DAC hat eine Auflösung von 10 Bit und der Schmalband-SFDR ist typischerweise größer als -78 dB.

Merkmale des AD9834 sind jeweils zwei Frequenz- und Phasenregister, um Frequenz- und Phasenmodulation zu unterstützen. Auch kann das Sinus-ROM überbrückt und der DAC vom Phasenakkumulator angesteuert werden, um eine Sägezahnfunktion zu erzeugen. Das Vorzeichen-Bit ist an einem Ausgangs-Pin verfügbar, sodass eine Rechteckwelle für ein Taktsignal generiert wird.

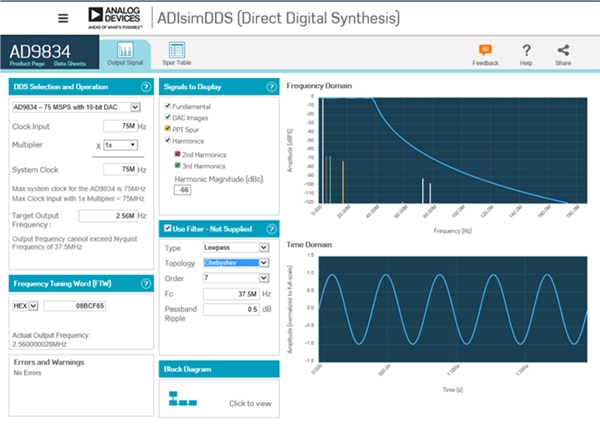

Die Hersteller verfügen zur Unterstützung des Entwicklungsprozesses oft über eine Auswahl von Tools, die die Aufgabe erleichtern. Der DDS AD9834 wird durch ADIsimDDS von Analog Devices, ein interaktives Online-Entwicklungstool, unterstützt, mit dem verschiedene Konfigurationen, z. B. Ausgangsfrequenzen, Abstimmungswörter und Taktreferenzen, evaluiert werden können (Abbildung 6).

Abbildung 6: Mithilfe des interaktiven Entwicklungstool ADIsimDDS von Analog Devices können verschiedene Konfigurationen des DDS und Filtermöglichkeiten getestet werden. (Bildquelle: Analog Devices)

Das Programm ADIsimDDS beginnt mit der Wahl eines spezifischen DDS-Produkts, in diesem Fall des AD9834. Der Benutzer gibt die Frequenz des Systemtakts und die gewünschte Ausgangsfrequenz ein, und das Programm berechnet das Abstimmungswort für den Phasenakkumulator. Auf einer Darstellung des Frequenzbereichs wird das Spektrum der DDS-Ausgabe einschließlich Ausgangssignal, Oberwellen des Ausgangssignals, DAC-Abbildern, Oberwellen und Abbildern der Taktfrequenz angezeigt. Auf die DDS-Ausgabe kann einer Filtersimulator angewendet werden, um die Auswirkungen verschiedener Filter auf das Ausgabespektrum beurteilen zu können.

Wenn eine bessere Leistung und höhere Frequenzen benötigt werden, kommt der AD9952YSVZ-REEL7 von Analog Devices mit einer maximalen Taktfrequenz von 400 MHz in Frage. Der Baustein kann sinusförmige Signale bis zu 200 MHz mit geringerem Phasenrauschen mit einer SFDR-Spezifikation von >80 dB bei 160 MHz (Versatz ±100 kHz) AOUT generieren. Im direkten Vergleich zum AD9834 liegt der Schmalband-SFDR bei typischen -70 dB bei 20 MHz, aber dies ist natürlich frequenzabhängig.

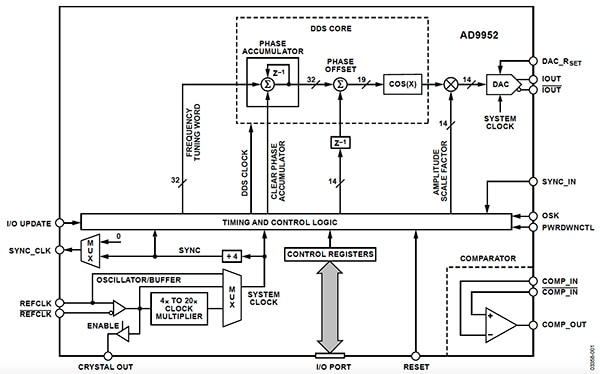

Der AD9952 hat keinen MCLK-Eingang. Er hat stattdessen einen eingebauten Oszillator für den Takt mit einem angeschlossenen PLL-Multiplizierer, der den Takt mithilfe eines einzelnen externen Quarzes mit Faktoren von 4 bis 20 multiplizieren kann (Abbildung 7). Wegen des eigenen Systemtakts von bis zu 400 MSPS kann der DDS ein niedriges Phasenrauschen von ≤ -120 dBc/Hz bei 1 kHz Versatz erreichen.

Abbildung 7: Der AD9952 generiert mit dem Eingang des externen Quarzes seinen eigenen Systemtakt und ist so in der Lage, die Bedingungen für eine höhere Leistung, z. B. niedriges Phasenrauschen, zu kontrollieren. (Bildquelle: Analog Devices)

Der AD9952 verfügt auch über einen 32 Bit tiefen Phasenakkumulator und über einen 14-Bit-DAC. Der DDS wird über eine serielle Schnittstelle gesteuert.

Für einen größeren Frequenzbereich gibt es den AD9957BSVZ-REEL von Analog Devices, der Taktfrequenzen bis zu 1 GHz mit Ausgangsfrequenzen bis zu 400 MHz für moderne Kommunikationsanwendungen unterstützt. Mit einer 32-Bit-Phasenakkumulator und einem sehr schnellen 14-Bit-DAC ist dieses Gerät als Quadraturmodulator bestimmt, der von acht Phasen-/Frequenz-Registern gesteuerte phasengleiche (I) und Quadratur-(Q)-Komponenten generiert. Quadraturmodulatoren generieren am Ausgang einen quadraturmodulierten Datenstrom. Zur Kompensierung der oben besprochenen sin(x)/x-Form ist ein optionaler SINC-Filter (sin(x)/x) verfügbar.

Diese drei Beispiele von im Handel erhältlichen DDS-ICs umfassen den Bereich von einfachen bis zu komplexen Signalgenerierungsaufgaben.

Fazit

Da von den Entwicklern immer neue Verbesserungen der Leistung und eine Verringerung der Abmessungen, der Kosten und des Energieverbrauchs von drahtlosen Systemen gefordert werden, erweisen sich DDS als hochwillkommen. Sie bringen digitale Stabilität, Flexibilität und Wiederholbarkeit für die Signalgenerierung und bieten mehrere Ausgangswellenformen und hochentwickelte Modulationsmöglichkeiten, einschließlich Frequenz- und Phasensprung. Da sie zum Standardwerkzeug des Entwicklers geworden sind, vereinfachen die Hersteller ebenfalls die Produktwahl und die Integration durch moderne Tools, die den Entwicklungsprozess verkürzen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.