Analog-Grundlagen - Teil 5: Bewältigung der Schwierigkeiten mit der Eingangsansteuerung von SAR-ADCs

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-10-28

Hinweis des Editors: Analog/Digital-Wandler (ADCs) verbinden die analoge mit der digitalen Welt und sind somit eine grundlegende Komponente jedes elektronischen Systems, das eine Verbindung zur realen Welt herstellt. Sie sind auch ein entscheidender Bestimmungsfaktor für die Leistung eines Systems. In dieser Reihe werden die Grundlagen der ADCs, ihre verschiedenen Arten und ihre Anwendung untersucht. Teil 1 dieser Serie über analoge Grundlagen diskutierte SAR-ADCs. Teil 2 befasst sich mit Delta-Sigma-Wandlern. Teil 3 befasst sich mit den Pipeline-ADCs. Teil 4 zeigt, wie Delta-Sigma-ADCs extrem rauscharme Ergebnisse erzielen können. Dieser 5. Teil befasst sich mit schwierigen Eingangs-Treiberfragen für SAR-ADCs.

Viele Datenerfassungs-, Industriesteuerungs- und Instrumentierungsanwendungen verwenden einen ultraschnellen Analog/Digital-Wandler (ADC), obwohl ein Analog/Digital-Wandler mit sukzessiver Approximation (SAR) perfekt geeignet wäre. Es muss jedoch unbedingt sichergestellt werden, dass die externe Schaltung um den SAR-Wandler ebenfalls der Aufgabe gewachsen ist, ein erfolgreiches Wandlungsergebnis zu gewährleisten. Die entscheidenden Anschlüsse, die besondere Sorgfalt für den SAR-Wandler erfordern, sind seine analogen Signaleingänge - wenn sie unbeaufsichtigt bleiben, können diese Eingangspins Stabilitätsprobleme und kapazitive Ladungsrückschläge („Kickback“) erzeugen, die zu ungenauen Wandlungen und verlängerter Signalerfassungszeit führen können.

Die Lösung zur präzisen Steuerung des Eingangssignals für SAR-Wandleranwendungen liegt in der Ansteuerung durch Operationsverstärker (Op-Amps). Diese Bauelemente, unterstützt durch die richtigen Werte für Ausgangswiderstand und Kondensator, bilden die Grundlage einer hochpräzisen, robusten Lösung für hochauflösende 16-Bit- und 20-Bit-SAR-Wandlersysteme.

In diesem Artikel werden kurz die Probleme erörtert, die mit der Erzielung stabiler und genauer SAR-ADC-Wandlungen verbunden sind. Anschließend wird ein geeigneter Operationsverstärker zur Ansteuerung eines SAR-ADCs vorgestellt und gezeigt, wie die erforderlichen Eingangstreiberschaltungen implementiert werden können. Als Beispiel werden Lösungen von Analog Devices verwendet.

SAR-ADC-Eingangskreis

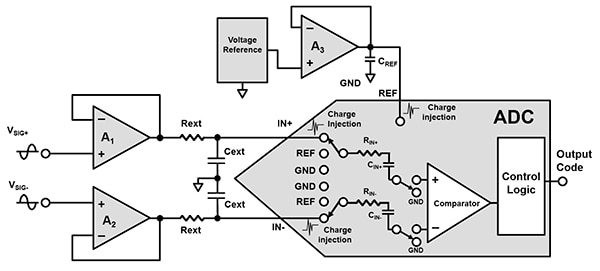

Die SAR-ADC-Treiberschaltungen verwenden Operationsverstärker (A1 und A2), die den ADC von ihren Signalquellen trennen (Abbildung 1). In dieser Schaltung hält Rext den Verstärker stabil, indem die Ausgangsstufe des Verstärkers von der kapazitiven ADC-Last (CIN+ und CIN-) und Cext „isoliert“ wird. Cext und CREF bieten eine nahezu perfekte Eingangsquelle für den ADC, die die Schaltladungsinjektion von den Eingangsanschlüssen IN+, IN- und REF absorbiert. Die Eingangsklemmen (IN+, IN-) folgen der Spannung des Eingangssignals (VSIG+, VSIG-) während der Erfassungszeit des Wandlers und laden die Eingangs-Abtastkondensatoren des ADCs, CIN+ und CIN-, auf.

Abbildung 1: In dieser Schaltung „isoliert“ Rext Cext von der Endstufe des Operationsverstärkers. Cext und CREF stellen Ladungsreservoirs für den differentiellen SAR-ADC während der Abtastperiode zur Verfügung. (Bildquelle: DigiKey)

Abbildung 1: In dieser Schaltung „isoliert“ Rext Cext von der Endstufe des Operationsverstärkers. Cext und CREF stellen Ladungsreservoirs für den differentiellen SAR-ADC während der Abtastperiode zur Verfügung. (Bildquelle: DigiKey)

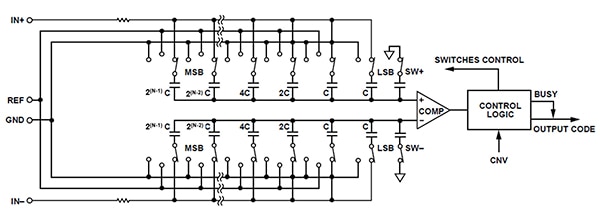

Wenn man sich das Innere des ADCs am Beispiel der SAR-ADCs AD7915 (16 Bit) und AD4021 (20 Bit) von Analog Device anschaut, kann man erkennen, dass ein Digital/Analog-Wandler (DAC) zur Ladungsumverteilung verwendet wird. Der kapazitive DAC hat zwei identische Anordnungen von binärgewichteten Kondensatoren. Diese Arrays werden an die nichtinvertierenden und invertierenden Komparatoreingänge angeschlossen (Abbildung 2).

Abbildung 2: Ein vereinfachtes auf den AD7915 und AD4021 basierendes Schema eines SAR-ADCs, wobei N gleich der Anzahl der Bits des Wandlers ist. (Bildquelle: Originalmaterial von Analog Devices, modifiziert von DigiKey)

Abbildung 2: Ein vereinfachtes auf den AD7915 und AD4021 basierendes Schema eines SAR-ADCs, wobei N gleich der Anzahl der Bits des Wandlers ist. (Bildquelle: Originalmaterial von Analog Devices, modifiziert von DigiKey)

Während der Erfassungsphase schalten die Eingänge (IN+ und IN-) auf das kapazitive Array um. Zusätzlich schließen SW+ und SW-, wobei die LSB-Kondensatoren (Least Significant Bit) mit Masse (GND) verbunden werden. In diesem Zustand werden die Kondensator-Arrays zu den Abtastkondensatoren, die die analogen Signale IN+ und IN- erfassen. Nach Abschluss der Abtastphase wird der CNV-Eingang zur Steuerlogik (rechte Seite) auf High-Pegel gezogen, um die Wandlungsphase einzuleiten.

Die Wamdlungsphase beginnt mit dem Öffnen von SW+ und SW- und dem Schalten der beiden Kondensatoranordnungen gegen GND. In dieser Konfiguration führt die erfasste Differenzspannung zwischen IN+ und IN- dazu, dass der Komparator unsymmetrisch wird. Der DAC für die Ladungsumverteilung schaltet methodisch jedes Element der Kondensatoranordnung vom höchstwertigen Bit (MSB) zum LSB, zwischen GND und REF. Der Komparatoreingang variiert durch binär gewichtete Spannungsstufen (VREF/2N-1, VREF/2N-2 ... VREF/4, VREF/2). Die Steuerlogik schaltet die Schalter von MSB auf LSB um, wodurch der Komparator wieder in einen ausgeglichenen Zustand gebracht wird. Nach Abschluss dieses Vorgangs kehrt der ADC in die Erfassungsphase zurück, und die Steuerlogik generiert den ADC-Ausgabecode.

Eingangsladungsinjektion, Schaltungsstabilität und Ansteuerung des ADCs AD7915

Ein kritischer Teil des Wandlungsprozesses ist die Erfassung einer genauen Eingangssignalspannung. Der ADC-Datenumwandlungsprozess läuft reibungslos ab, wenn der Treiberverstärker die Eingangskondensatoren CIN+ und CIN- genau auflädt und dabei bis zum Ende der ADC-Erfassungszeit stabil bleibt. Das Problem für die Entwickler besteht darin, dass der Eingangsanschluss des ADCs eine Kapazität (CIN+, CIN-) sowie Schaltrauschen oder „Kickback“-Ladungsinjektionen einführt, die der Treiberverstärker bewältigen muss.

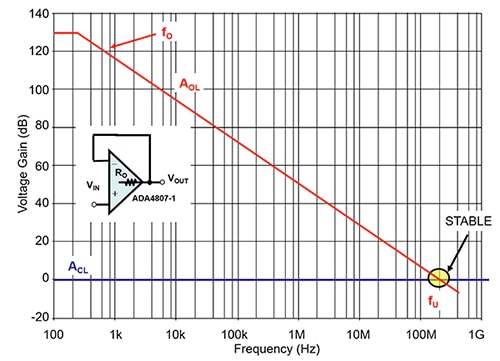

Ein Bode-Plot der Verstärkerschaltung schätzt schnell die Stabilität der Schaltung ab. Das Bode-Plot-Tool approximiert die Größenordnung der Verstärkungsübertragungsfunktionen eines Verstärkers im offenen und geschlossenen Regelkreis (Abbildung 3).

Abbildung 3: Die Übertragungsfunktion im offenen und geschlossenen Regelkreis des Verstärkers in Abbildung 1, ohne Rext und Cext als Verstärkerlasten und den folgenden SAR-ADC. (Bildquelle: DigiKey)

Abbildung 3: Die Übertragungsfunktion im offenen und geschlossenen Regelkreis des Verstärkers in Abbildung 1, ohne Rext und Cext als Verstärkerlasten und den folgenden SAR-ADC. (Bildquelle: DigiKey)

Die y-Achse quantifiziert die Open-Loop-Verstärkung (AOL, Verstärkung im offenen Regelkreis) des Verstärkers und die Closed-Loop-Verstärkung (ACL, Verstärkung im geschlossenen Regelkreis) der Verstärkerschaltung, wobei die AOL-Kurve des Verstärkers bei 130 Dezibel (dB) beginnt und die Closed-Loop-Verstärkung (ACL) gleich 0 dB ist. Die Einheiten entlang der x-Achse quantifizieren logarithmisch die Verstärkungsfrequenz im offenen und geschlossenen Regelkreis von 100 Hertz (Hz) bis 1 Gigahertz (GHz).

In Abbildung 3 schreitet die Gleichstrom-Steuerkreisverstärkung des Verstärkers bei etwa 220 Hz (fO) von 130 dB mit einer Rate von -20 dB/Dekade nach unten fort. Wenn die Frequenz zunimmt, setzt sich diese Dämpfungsrate bei etwa 180 Megahertz (MHz) über 0 dB hinaus fort. Da diese Kurve ein einpoliges System darstellt, ist die Übergangsfrequenz fU gleich dem Verstärkungs-Bandbreiten-Produkt (GBWP) des verstärkungsstabilen Verstärkers. Dieses Diagramm stellt ein stabiles System dar, da die AOL- und ACL-Verschlussrate 20 dB/Dekade beträgt.

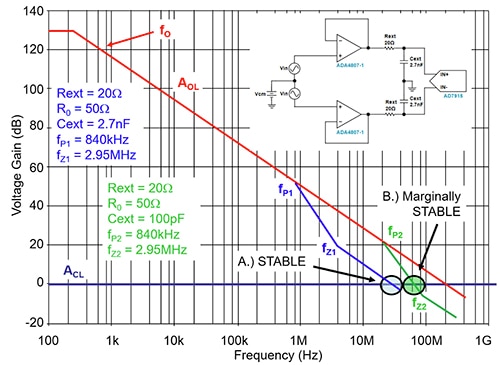

Das Hinzufügen von Rext und Cext und des SAR-ADC modifiziert die Verstärkerschaltung, indem sie einen Systemnullpunkt und -pol erzeugt (Abbildung 4). Das System besteht aus einem 16-Bit-Differential-PulSAR-ADC AD7915 mit 1 Megasample pro Sekunde (MS/s) und einem Rail-to-Rail-Eingangs-/Ausgangsverstärker ADA4807-1 mit 180 MHz, beide von Analog Devices. Die Kombination aus Verstärker und ADC erfordert Rext aufgrund der 30 Picofarad (pF) (typisch) ADC-Eingangskapazitätsbelastung. Die Schaltung erfordert außerdem, dass Cext als Ladungsspeicher fungiert, um am ADC-Eingang genügend Ladung zur Verfügung zu stellen, um genau der Eingangsspannung zu entsprechen.

Abbildung 4: Gezeigt ist die Bode-Plot-Antwort von zwei ADA4807-Operationsverstärkern, die den SAR-ADC AD7915 mit zwei separaten Rext/Cext-Paaren ansteuern. Die Eckfrequenzen fP1 und fZ1 modifizieren die Open-Loop-Verstärkung des Verstärkers, wodurch ein stabiles Systemverhalten erzeugt wird. Die Eckfrequenzen fP2 und fZ2 modifizieren die Open-Loop-Verstärkung des Verstärkers, wodurch ein gering stabiles Systemverhalten erzeugt wird. (Bildquelle: DigiKey)

Abbildung 4: Gezeigt ist die Bode-Plot-Antwort von zwei ADA4807-Operationsverstärkern, die den SAR-ADC AD7915 mit zwei separaten Rext/Cext-Paaren ansteuern. Die Eckfrequenzen fP1 und fZ1 modifizieren die Open-Loop-Verstärkung des Verstärkers, wodurch ein stabiles Systemverhalten erzeugt wird. Die Eckfrequenzen fP2 und fZ2 modifizieren die Open-Loop-Verstärkung des Verstärkers, wodurch ein gering stabiles Systemverhalten erzeugt wird. (Bildquelle: DigiKey)

Der Schaltkreis in Abbildung 4 kann aufgrund der kapazitiven ADC-Last und der Schaltladungsinjektion des ADCs bei der Ersterfassung potentiell schwingen. Der zusätzliche Pol und Nullpunkt, der durch die Ausgangskomponenten des Rext/Cext-Verstärkers erzeugt wird, gewährleisten ein stabiles System, so dass der Schnittpunkt der Verstärkungskurve bei offenem und geschlossenem Regelkreis größer als 20 dB/Dekade ist, was einen Phasenspielraum von weniger als 45° ergibt. Diese Konfiguration mit fP2 und fZ2 erzeugt eine instabile Schaltung.

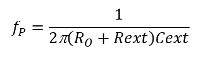

Um Instabilität zu vermeiden, müssen Entwickler bei der Bewertung der Open-Loop-Verstärkungskurve des Verstärkers mit Rext und Cext in der Schaltung den Effekt des Open-Loop-Ausgangswiderstands des Verstärkers, RO, berücksichtigen. Die Kombination von RO mit 50 Ohm (Ω), Rext und Cext modifiziert die Open-Loop-Kennlinie durch Einführung eines Pols (fP, Gleichung 1) und einer Nullstelle (fZ, Gleichung 2). Die Werte RO, Rext und Cext bestimmen die Eckfrequenz von fP. Die Werte von Rext und Cext bestimmen die Nullstellen-Eckfrequenz, fZ.

Gleichung 1

Gleichung 1

Gleichung 2

Gleichung 2

Die fP- und fZ-Berechnungen sind:

fP1 = 842 kHz

fZ1 = 2,95 MHz

mit: RO = 50 Ω

Rext = 20 Ω

Cext = 2,7 Nanofarad (nF)

fP2 = 22,7 MHz

fZ2 = 79,5 MHz

mit: RO = 50 Ω

Rext = 20 Ω

Cext = 0,1 Nanofarad (nF)

Die obigen Werte für fP1 und fZ1 bieten ein stabiles System für die AD7915 und ADA4807-1.

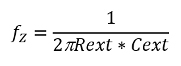

Verwendung des SAR-ADCs Easy Drive AD4021

Eine Alternative zum AD7915 ist der 20 Bit Easy-Drive-SAR-Wandler AD4021 für 1 MS/s. Die Bausteinfamilie AD4021 reduziert den Eingangs-Kickback und den Eingangsstrom erheblich auf 0,5 Mikroampere (μA)/(MS/s). Der Easy Drive zeichnet sich durch einen reduzierten Stromverbrauch und eine reduzierte Komplexität der Signalkette aus.

Der Analogeingang des AD4021 verfügt über eine Schaltung, die den typischen nichtlinearen Kickback (Ladungsrückschlag) am Schaltkondensator-SAR-Eingang reduziert. Die Reduzierung des Kickbacks und eine längere Erfassungsphase ermöglichen die Verwendung von Treiberverstärkern mit geringerer Bandbreite und Leistung (Abbildung 5).

Abbildung 5: Die Eingangsschaltung und das Erfassungs-Timing des AD4021 reduzieren den Kickback-Schaltstrom und lockern die strengen Anforderungen des Treiberverstärkers. (Bildquelle: Analog Devices)

Abbildung 5: Die Eingangsschaltung und das Erfassungs-Timing des AD4021 reduzieren den Kickback-Schaltstrom und lockern die strengen Anforderungen des Treiberverstärkers. (Bildquelle: Analog Devices)

Die Kombination aus Kickback-Reduzierung und längerer Erfassungszeit ermöglicht auch einen größeren Rext-Widerstandswert im Eingangswiderstands-Kondensator-Filter (RC-Filter) und einen entsprechend kleineren Cext-Kondensator. Diese Kombination aus einer kleineren Cext-Verstärkerlast verbessert die Stabilität und senkt die Verlustleistung.

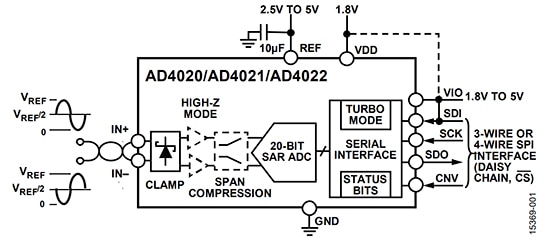

Das empfohlene Anschlussschema für den AD4021 mit einer einzigen 5-Volt-Versorgung scheint ein ähnliches Schaltbild zu haben. Die Anforderungen an den Verstärker sind jedoch gelockert, und die Rext/Cext (R und C)-Werte sind kleiner (Abbildung 6).

Abbildung 6: Typisches Anwendungsdiagramm für die AD4021 und ADA4807-1, die mit einer einzigen 5-Volt-Versorgung betrieben werden, mit entspannteren Verstärkeranforderungen und einem größeren Rext-Wert im Vergleich zur Ansteuerung des zuvor besprochenen AD7915. (Bildquelle: Analog Devices)

Abbildung 6: Typisches Anwendungsdiagramm für die AD4021 und ADA4807-1, die mit einer einzigen 5-Volt-Versorgung betrieben werden, mit entspannteren Verstärkeranforderungen und einem größeren Rext-Wert im Vergleich zur Ansteuerung des zuvor besprochenen AD7915. (Bildquelle: Analog Devices)

In Abbildung 6 verwendet der SAR-basierte AD4021 auch einen DAC zur Ladungsumverteilung. Der ADC verfügt über einen integrierten Wandlungstakt und einen seriellen Taktgeber. Folglich erfordert der Wandlungsprozess keinen Eingang für einen synchronen Takt (SCK). Diese Taktkonfiguration ermöglicht die Verlängerung der Erfassungszeit, wodurch die Genauigkeit verbessert wird, da mehr Zeit zur Verfügung steht, damit sich das Eingangssignal auf einen Endwert einpendeln kann.

Die Hauptüberlegung für den Treiberverstärker sowohl für den AD7915 als auch für den AD4021 ist das Rauschen, da sich die Kombination Verstärker/Rext/Cext von einem Vollaussteuerungsschritt auf einen 16-Bit-Pegel (0,0015%, 15 ppm) für den AD7915 und einen 20-Bit-Pegel (0,00001%, 1 ppm) für den AD4021 einpendeln muss.

Um die Signal-zu-Rauschen-Performance (SNR) der AD7915 und AD4021 zu erhalten, muss das Rauschen des Treiberverstärkers weniger als ein Drittel des Rauschens des ADC betragen. Wenn das AD4021-Rauschen 60 Mikrovolt effektiv (mVeff) beträgt, muss das Rauschen der Kombination Verstärker/Rext/Cext weniger als 20 mVeff betragen. Beträgt das AD4021-Rauschen 31,5 Mikrovolt effektiv (mVeff) , muss das Rauschen der Kombination Verstärker/Rext/Cext weniger als 10,5 mVeff betragen.

Mit dem Precision ADC Driver Tool von Analog Devices können Entwickler schnell die richtigen Rext- und Cext-Werte berechnen. Mit einem ausgewählten Treiber und ADC modelliert dieses Tool die Einschwingzeit, das Rauschen und das Verzerrungsverhalten der Schaltung.

Fazit

Der SAR-ADC dominiert nach wie vor Anwendungen in den Bereichen Ultrahighspeed-Datenerfassung, industrielle Steuerung und Instrumentierung. Die externe Eingangsschaltung für diese Bauelemente - der Treiberverstärker und der Eingangsfilter - erfordert jedoch besondere Aufmerksamkeit, um mögliche Probleme der Schaltladungsinjektion und der Verstärkerstabilität zu berücksichtigen.

Die Lösung zur präzisen Steuerung des Eingangssignals für die meisten SAR-Wandler, wie z.B. AD7916 und AD4021, liegt im Operationsverstärker-Treiber - in diesem Fall dem ADA4807-1. Diese Bauelemente, unterstützt durch die richtigen Werte für Ausgangswiderstand und Kondensator, bilden die Grundlage einer hochpräzisen, robusten Lösung für hochauflösende 16-Bit- und 20-Bit-SAR-Wandlersysteme.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.