Beschleunigung von KI-Anwendungen auf dem Evaluierungskit VCK190 von Xilinx mit den IP-Kernen von Design Gateway

2022-11-18

Die Bausteine der Serie Versal AI Core von Xilinx wurden entwickelt, um das einzigartige und äußerst schwierige Problem der KI-Inferenz (Schlussfolgerung) zu lösen, indem ein KI-Rechenkern der ASIC-Klasse mit hoher Recheneffizienz zusammen mit einer flexiblen programmierbaren Struktur verwendet wird, um eine KI-Anwendung mit Beschleunigern aufzubauen, die den Wirkungsgrad für jede beliebige Arbeitslast maximieren und gleichzeitig einen niedrigen Stromverbrauch und geringe Latenz liefern.

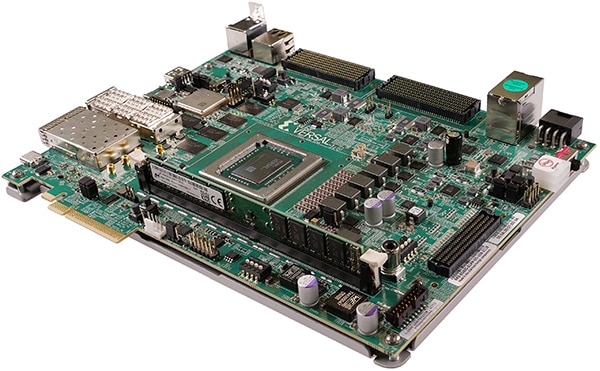

Das Evaluierungskit VCK190 für die Serie Versal AI Core enthält den Baustein VC1902, der die beste KI-Performance im Portfolio aufweist. Das Kit ist für Entwicklungen gedacht, die eine leistungsstarke Performance bei der KI-Inferenz und Signalverarbeitung erfordern. Mit einer 100-mal höheren Rechenleistung als aktuelle CPUs in der Server-Klasse und verschiedenen Verbindungsoptionen ist das VCK190-Kit eine ideale Evaluierungs- und Prototyping-Plattform für eine Vielzahl von Anwendungen von der Cloud bis zur verteilten Datenverarbeitung (Edge).

Abbildung 1: Evaluierungskit VCK190 von Xilinx für die Serie Versal AI Core. (Bildquelle: AMD, Inc)

Abbildung 1: Evaluierungskit VCK190 von Xilinx für die Serie Versal AI Core. (Bildquelle: AMD, Inc)

Hauptmerkmale des Evaluierungskits VCK190

- Onboard-Komponente der Serie Versal AI Core

- Ausgestattet mit Versal-ACAP-Chip XCVC1902

- KI- und DSP-Engines bieten 100-mal höhere Rechenleistung als heutige CPUs der Server-Klasse

- Vorgefertigte Referenzdesigns von Partnern ermöglichen schnelles Prototyping

- Neueste Vernetzungstechnologie für die Entwicklung von hochmodernen Anwendungen

- Integrierte PCIe®-Gen4-Hard-IP für leistungsstarke Geräteschnittstellen wie NVMe-SSD und Host-Prozessoren

- Eingebaute 100G-EMAC-Hard-IP für Highspeed-100G-Netzwerkschnittstellen

- DDR4- und LPDDR4-Speicherschnittstellen

- Ko-optimierte Tools und Debug-Methode

- Vivado® ML, einheitliche Software-Plattform Vitis™, Vitis AI, KI-Engine-Tools für die Entwicklung von KI-Inferenzanwendungen

KI-Schnittstellenbeschleunigung mit den Bausteinen der Serie Versal AI Core von Xilinx

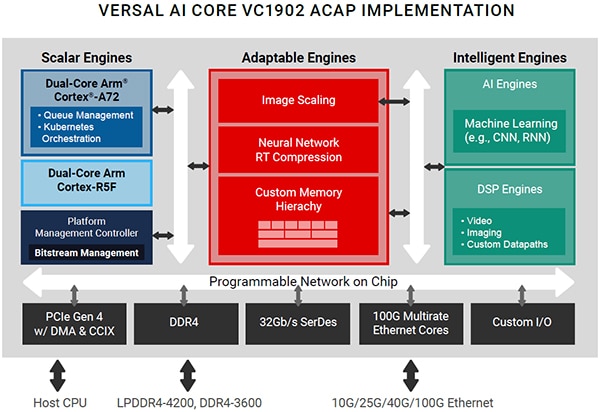

Abbildung 2: Blockdiagramm der ACAP-Komponente Versal AI Core VC1902 von Xilinx. (Bildquelle: AMD, Inc)

Abbildung 2: Blockdiagramm der ACAP-Komponente Versal AI Core VC1902 von Xilinx. (Bildquelle: AMD, Inc)

Die „Adaptive Compute Acceleration Platform“ (ACAP) der Serie Versal® AI Core ist eine hochintegrierte, heterogene Multicore-Komponente, die sich auf Hardware- und Softwareebene dynamisch an eine Vielzahl von KI-Workloads anpassen kann und sich damit ideal für Anwendungen im Bereich KI-Edge-Computing oder für Cloud-Beschleunigerkarten eignet. Die Plattform integriert skalare Engines der nächsten Generation für eingebettete Berechnungen, adaptive Engines für Hardwareflexibilität und intelligente Engines, bestehend aus DSP-Engines und revolutionären KI-Engines für Inferenz und Signalverarbeitung. Das Ergebnis ist ein anpassungsfähiger Beschleuniger, der die Performance, Latenz und Energieeffizienz herkömmlicher FPGAs und GPUs für KI/ML-Workloads übertrifft.

Hauptmerkmale der Versal-ACAP-Plattform

- Adaptive Engines:

- Angepasste Speicherhierarchie optimiert Datenbewegung und -verwaltung für Beschleunigerkernel

- Vor- und Nachbearbeitungsfunktionen, einschließlich RT-Komprimierung durch neuronale Netze und Bildskalierung

- KI-Engines (DPU):

- Geschachteltes Array aus Vektorprozessoren, bis zu 133 INT8 TOPS Leistung mit XCVC1902 Bausteinen, genannt „Deep Learning Processing Unit“ oder DPU

- Ideal für neuronale Netze wie CNN, RNN und MLP; die Hardware ist anpassbar, um sie für sich entwickelnde Algorithmen zu optimieren

- Skalare Engines:

- Quad-Core-ARM-Prozessor-Subsystem, Plattform-Management-Controller für Sicherheits-, Energie- und Bitstream-Management

KI-Inferenzleistung des VCK190

Der VCK190 bietet im Vergleich zu aktuellen Server-CPUs eine über 100-fach höhere Rechenleistung. Nachfolgend finden Sie ein Beispiel für die Performance auf der Grundlage der KI-Engine-Implementierung durch den DPU-Core C32B6 mit Batch = 6. In der folgenden Tabelle finden Sie die Durchsatzleistung (in Frames/Sek. oder fps) für verschiedene neuronale Netzwerkbeispiele auf dem VCK190 mit der DPU betrieben bei 1250 MHz.

|

Tabelle 1: Beispiel für die KI-Inferenzleistung des VCK190.

Weitere Einzelheiten zur KI-Performance des VCK190 finden Sie im Vitis AI Library User Guide (UG1354), r2.5.0 unter https://docs.xilinx.com/r/en-US/ug1354-xilinx-ai-sdk/VCK190-Evaluation-Board

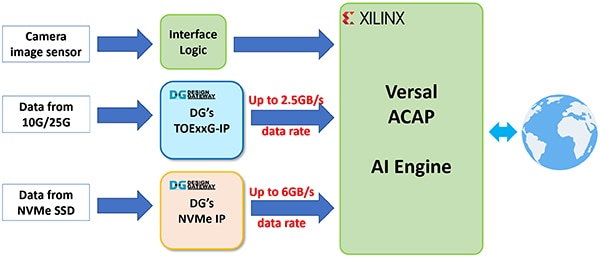

Wie beschleunigen die IP-Kerne von Design Gateway die Performance von KI-Anwendungen?

Die IP-Kerne von Design Gateway sind so konzipiert, dass sie Netzwerk- und Datenspeicherprotokolle ohne CPU-Eingriff verarbeiten können. Dies macht es ideal, um CPU-Systeme vollständig von der komplizierten Protokollverarbeitung zu entlasten und sie in die Lage zu versetzen, den größten Teil ihrer Rechenleistung für KI-Anwendungen zu nutzen, einschließlich KI-Inferenz, Vor- und Nachverarbeitung von Daten, Benutzeroberfläche, Netzwerkkommunikation und Datenspeicherzugriff, um die bestmögliche Leistung zu erzielen.

Abbildung 3: Blockdiagramm eines Beispiels einer KI-Anwendung mit IP-Kernen von Design Gateway. (Bildquelle: Design Gateway)

Abbildung 3: Blockdiagramm eines Beispiels einer KI-Anwendung mit IP-Kernen von Design Gateway. (Bildquelle: Design Gateway)

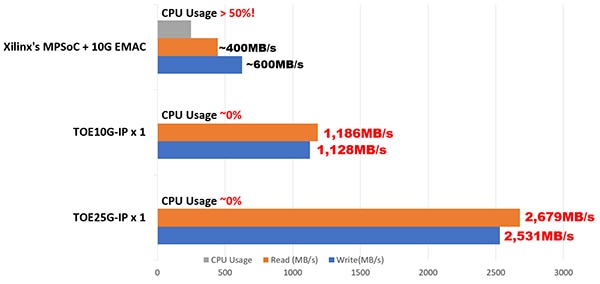

Performance der TCP Offload Engine IP (TOExxG-IP) von Design Gateway

Die Verarbeitung von Highspeed-TCP-Datenströmen mit hohem Durchsatz über 10GbE oder 25GbE durch herkömmliche CPU-Systeme erfordert mehr als 50 % der CPU-Zeit, was die Gesamtleistung von KI-Anwendungen verringert. Laut dem 10G-TCP-Leistungstest auf den MPSoC-Linux-Systemen von Xilinx beträgt die CPU-Auslastung während der 10GbE-TCP-Übertragung mehr als 50 %, für die Übertragungsgeschwindigkeit von TCP-Sende- und -Empfangsdaten konnte nur etwa 40 % bis 60 % der 10GbE-Geschwindigkeit oder 400 MB/s bis 600 MB/s erreicht werden.

Durch die Implementierung des TOExxG-IP-Core von Design Gateway kann die CPU-Auslastung für TCP-Übertragungen über 10GbE und 25GbE auf nahezu 0 % reduziert werden, während die Ethernet-Bandbreite zu nahezu 100 % genutzt werden kann. Dies ermöglicht das Senden und Empfangen von Daten über das TCP-Netzwerk direkt durch reine Hardware-Logik und wird in die Versal AI Engine mit minimaler CPU-Belastung und der geringstmöglichen Latenz eingespeist. Abbildung 4 unten zeigt den Vergleich der CPU-Auslastung und der TCP-Übertragungsgeschwindigkeit zwischen TOExxG-IP und MPSoC-Linux-Systemen.

Abbildung 4: Leistungsvergleich der 10G/25G-TCP-Übertragung durch MPSoC-Linux-Systeme und den TOExxG-IP-Core von Design Gateway. (Bildquelle: Design Gateway)

Abbildung 4: Leistungsvergleich der 10G/25G-TCP-Übertragung durch MPSoC-Linux-Systeme und den TOExxG-IP-Core von Design Gateway. (Bildquelle: Design Gateway)

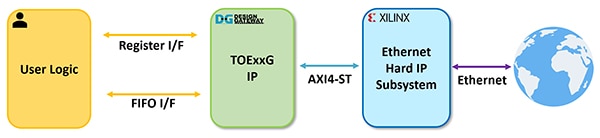

TOExxG-IP von Design Gateway für Versal-Komponenten

Abbildung 5: Übersicht der TOExxG-IP-Systeme. (Bildquelle: Design Gateway)

Abbildung 5: Übersicht der TOExxG-IP-Systeme. (Bildquelle: Design Gateway)

Der TOE100G-IP-Kern implementiert den TCP/IP-Stack (in festverdrahteter Logik) und ist mit dem 100-Gb-Ethernet-Subsystem-Modul von Xilinx für die untere Hardware-Schicht verbunden. Die Benutzerschnittstelle des TOExxG-IP besteht aus einer Registerschnittstelle für Steuersignale und einer FIFO-Schnittstelle für Datensignale. Der TOExxG-IP ist für die Verbindung mit dem Ethernet-Subsystem von Xilinx über die AXI4-ST-Schnittstelle konzipiert. Die Taktfrequenz der Benutzeroberfläche hängt von der Geschwindigkeit der Ethernet-Schnittstelle ab (z. B. 156,625 MHz oder 322,266 MHz).

Merkmale des TOExxG-IP

- Vollständige TCP/IP-Stack-Implementierung ohne Bedarf an der CPU

- Unterstützt eine Session mit einem TOExxG-IP

- Multi-Session kann durch Verwendung mehrerer TOExxG-IP-Instanzen realisiert werden

- Unterstützt sowohl den Server- als auch den Client-Modus (passives/aktives Öffnen und Schließen)

- Unterstützt Jumbo-Frame

- Einfache Datenschnittstelle durch Standard-FIFO-Schnittstelle

- Einfache Steuerschnittstelle durch Single-Port-RAM-Schnittstelle

Die Nutzung der FPGA-Ressourcen auf dem FPGA-Baustein XCVC1902-VSVA2197-2MP-ES ist in Tabelle 2 dargestellt.

|

Tabelle 2: Beispiel-Implementierungsstatistik für Versal-Komponenten.

Weitere Details zum TOExxG-IP sind im Datenblatt beschrieben, das auf der Website von Design Gateway unter den folgenden Links heruntergeladen werden kann:

- Xilinx-Datenblatt für den TOE10G-IP-Kern

- Xilinx-Datenblatt für den TOE25G-IP-Kern

- Xilinx-Datenblatt für den TOE100G-IP-Kern

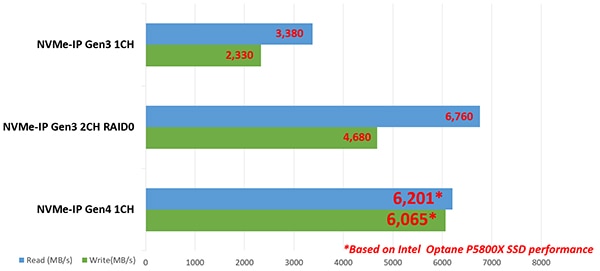

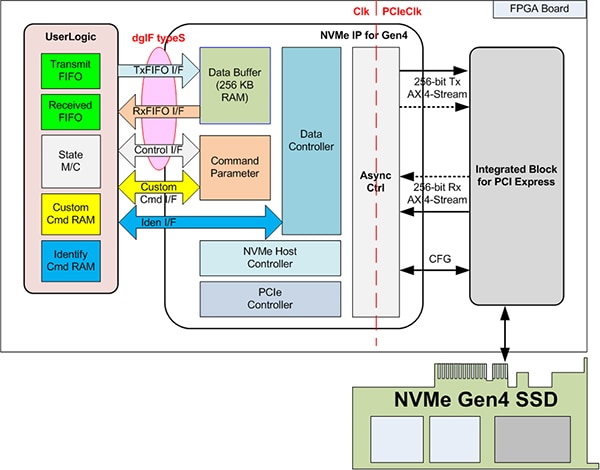

Performance des NVMe-Hostcontroller-IP von Design Gateway

Die NVMe-Speicherschnittstelle mit PCIe Gen3 x4 oder PCIe Gen4 x4 bietet Datenraten von bis zu 32 Gbit/s und 64 Gbit/s. Dies ist drei- bis sechsmal höher als die 10GbE-Ethernet-Geschwindigkeit. Die Verarbeitung des komplizierten NVMe-Speicherprotokolls durch die CPU, um die höchstmögliche Festplattenzugriffsgeschwindigkeit zu erreichen, erfordert mehr CPU-Zeit als das TCP-Protokoll über 10GbE.

Design Gateway löste dieses Problem durch die Entwicklung des NVMe-IP-Kerns, der als eigenständiger NVMe-Hostcontroller ausgeführt werden kann und in der Lage ist, ohne CPU direkt mit einer NVMe-SSD zu kommunizieren. Dies ermöglicht eine hohe Effizienz und Leistung des NVMe-PCIe-Gen3- und -Gen4-SSD-Zugriffs, was die Benutzeroberfläche und die Standardfunktionen für eine einfache Nutzung vereinfacht, ohne dass Kenntnisse des NVMe-Protokolls erforderlich sind. Die Performance von NVMe-PCIe-Gen4-SSDs kann mit NVMe-IP eine Übertragungsgeschwindigkeit von bis zu 6 GB/s erreichen, wie in Abbildung 6 dargestellt.

Abbildung 6: Leistungsvergleich von NVMe-PCIe-Gen3- und -Gen4-SSD mit dem NVMe-IP-Kern von Design Gateway. (Bildquelle: Design Gateway)

Abbildung 6: Leistungsvergleich von NVMe-PCIe-Gen3- und -Gen4-SSD mit dem NVMe-IP-Kern von Design Gateway. (Bildquelle: Design Gateway)

NVMe-IPs von Design Gateway für Versal-Geräte

Abbildung 7: Übersicht über NVMe-IP-Systeme. (Bildquelle: Design Gateway)

Abbildung 7: Übersicht über NVMe-IP-Systeme. (Bildquelle: Design Gateway)

Merkmale von NVMe-IP

- Kann die Anwendungsschicht, die Transaktionsschicht, die Datenverbindungsschicht und einige Teile der physischen Schicht implementieren, um auf die NVMe-SSD ohne CPU oder externen DDR-Speicher zuzugreifen

- Arbeitet mit Xilinx-PCIe-Gen3- und -Gen4-Hard-IP

- Die Möglichkeit, BRAM und URAM als Datenpuffer zu nutzen, ohne eine externe Speicherschnittstelle zu benötigen

- Unterstützt sechs Befehle: Identifizieren, Abschalten, Schreiben, Lesen, SMART und Flush (optionale Unterstützung zusätzlicher Befehle möglich)

Die Nutzung der FPGA-Ressourcen auf dem FPGA-Baustein XCVC1902-VSVA2197-2MP-E-S ist in Tabelle 2 dargestellt.

|

Tabelle 3: Beispiel-Implementierungsstatistik für Versal-Komponenten.

Weitere Einzelheiten zum NVMe-IP für den Versal-Baustein sind im Datenblatt beschrieben, das von der Website von Design Gateway unter dem unten stehenden Link heruntergeladen werden kann:

Datenblatt zum NVMe-IP-Kern für Gen4 von Xilinx

Fazit

Sowohl der TOExxG-IP- als auch der NVMe-IP-Kern könnten dazu beitragen, die Performance von KI-Anwendungen zu beschleunigen, indem CPU-Systeme vollständig von rechen- und speicherintensiven Protokollen wie TCP und NVMe-Speicherprotokollen entlastet werden, was für Echtzeit-KI-Anwendungen entscheidend ist. Dadurch können die Bausteine der Serie Versal AI Core von Xilinx KI-Inferenz- und leistungsstarke Rechenanwendungen ohne Engpässe oder Verzögerungen bei der Verarbeitung von Netzwerk- und Datenspeicherprotokollen durchführen.

Das Evaluierungskit VCK190 und die Netzwerk- und Speicher-IP-Lösung von Design Gateway ermöglichen die bestmögliche Performance in KI-Anwendungen bei geringstmöglicher FPGA-Ressourcennutzung und sehr hoher Energieeffizienz auf dem Versal AI Core von Xilinx.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.